74HCT280D

74HCT280D is 9-bit odd/even parity generator/checker manufactured by Nexperia.

- Part of the 74HC280 comparator family.

- Part of the 74HC280 comparator family.

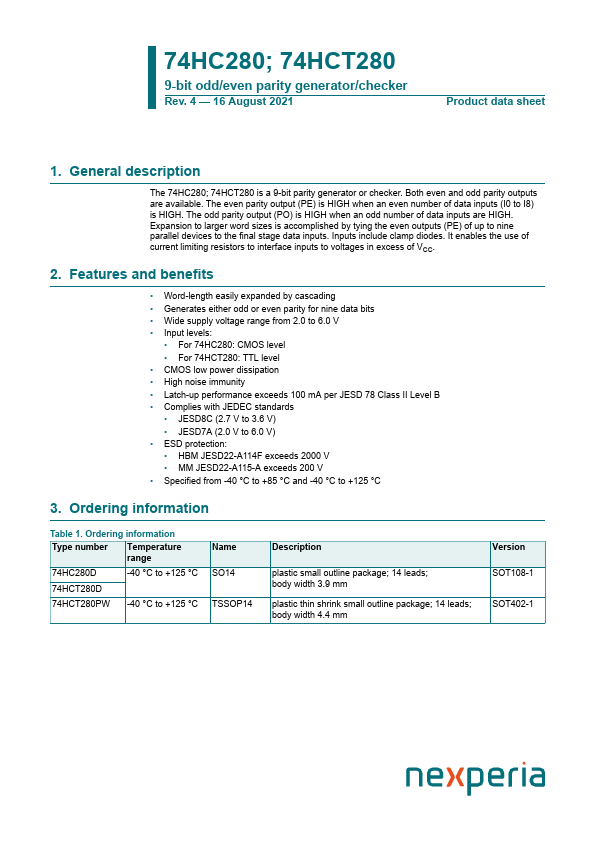

74HC280; 74HCT280

9-bit odd/even parity generator/checker

Rev. 4

- 16 August 2021

Product data sheet

1. General description

The 74HC280; 74HCT280 is a 9-bit parity generator or checker. Both even and odd parity outputs are available. The even parity output (PE) is HIGH when an even number of data inputs (I0 to I8) is HIGH. The odd parity output (PO) is HIGH when an odd number of data inputs are HIGH. Expansion to larger word sizes is acplished by tying the even outputs (PE) of up to nine parallel devices to the final stage data inputs. Inputs include clamp diodes. It enables the use of current limiting resistors to interface inputs to voltages in excess of VCC.

2. Features and...