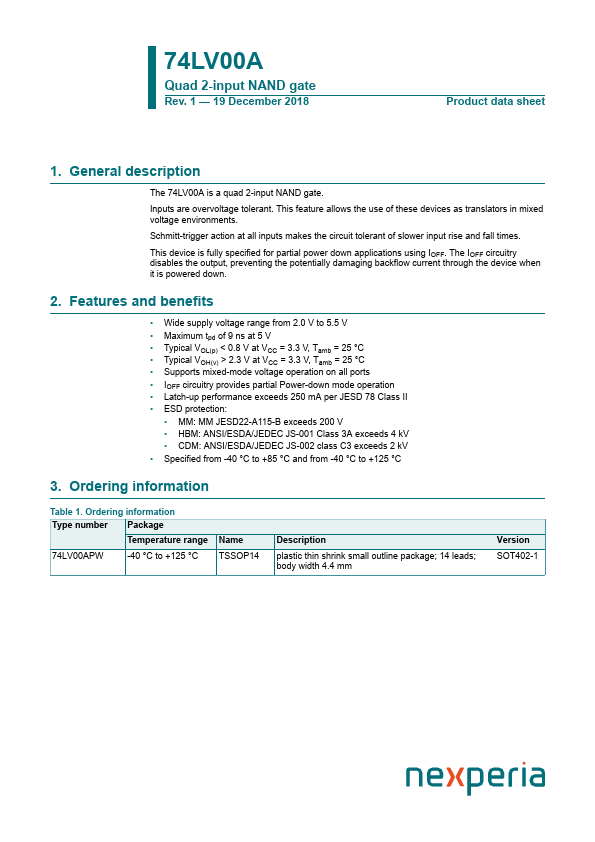

74LV00A

Overview

The 74LV00A is a quad 2-input NAND gate. Inputs are overvoltage tolerant.

- Features and benefits

- Wide supply voltage range from 2.0 V to 5.5 V

- Maximum tpd of 9 ns at 5 V

- Typical VOL(p) < 0.8 V at VCC = 3.3 V, Tamb = 25 °C

- Typical VOH(v) > 2.3 V at VCC = 3.3 V, Tamb = 25 °C

- Supports mixed-mode voltage operation on all ports

- IOFF circuitry provides partial Power-down mode operation

- Latch-up performance exceeds 250 mA per JESD 78 Class II

- ESD protection:

- MM: MM JESD22-A115-B exceeds 200 V