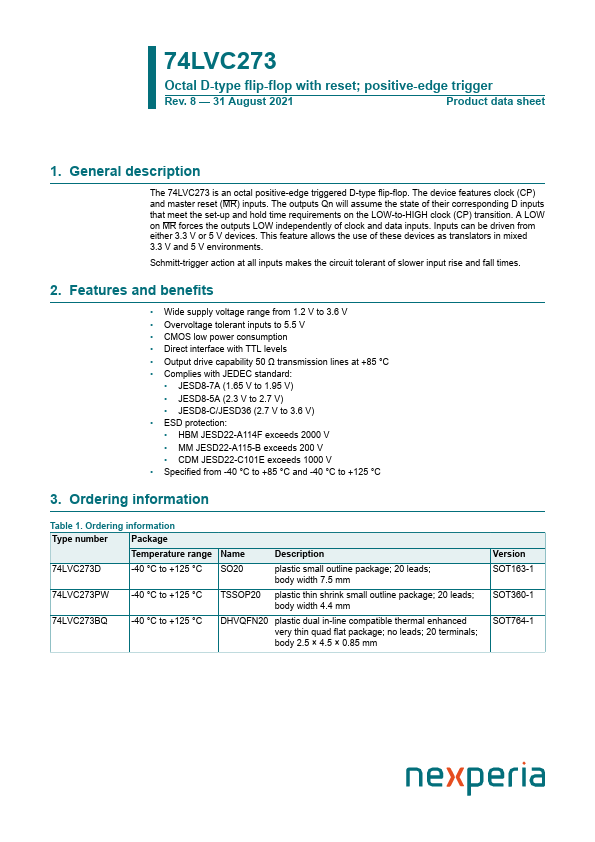

74LVC273

74LVC273 is Octal D-type flip-flop manufactured by Nexperia.

Octal D-type flip-flop with reset; positive-edge trigger

Rev. 8

- 31 August 2021

Product data sheet

1. General description

The 74LVC273 is an octal positive-edge triggered D-type flip-flop. The device Features clock (CP) and master reset (MR) inputs. The outputs Qn will assume the state of their corresponding D inputs that meet the set-up and hold time requirements on the LOW-to-HIGH clock (CP) transition. A LOW on MR forces the outputs LOW independently of clock and data inputs. Inputs can be driven from either 3.3 V or 5 V devices. This feature allows the use of these devices as translators in mixed 3.3 V and 5 V environments.

Schmitt-trigger action at all inputs makes the...