Datasheet Summary

8-bit shift register with output register

Rev. 4

- 3 September 2020

Product data sheet

1. General description

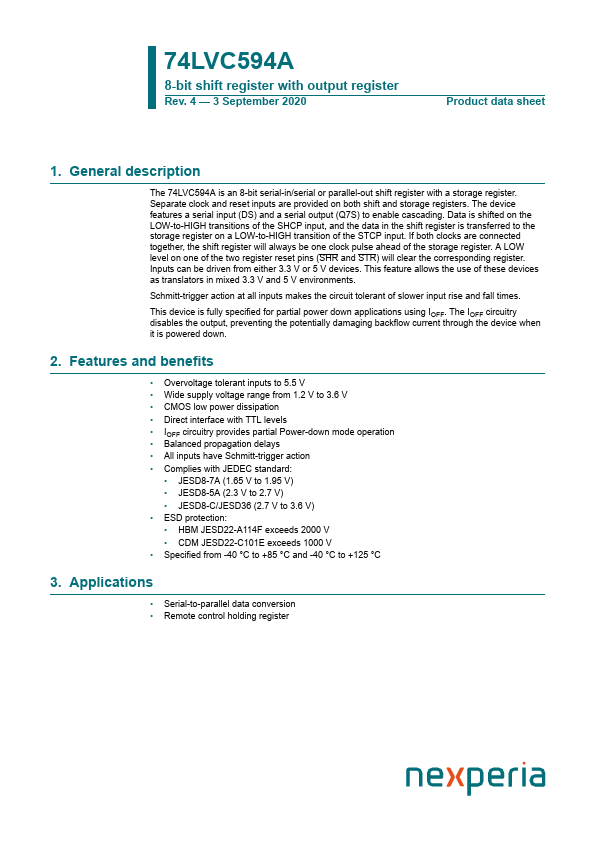

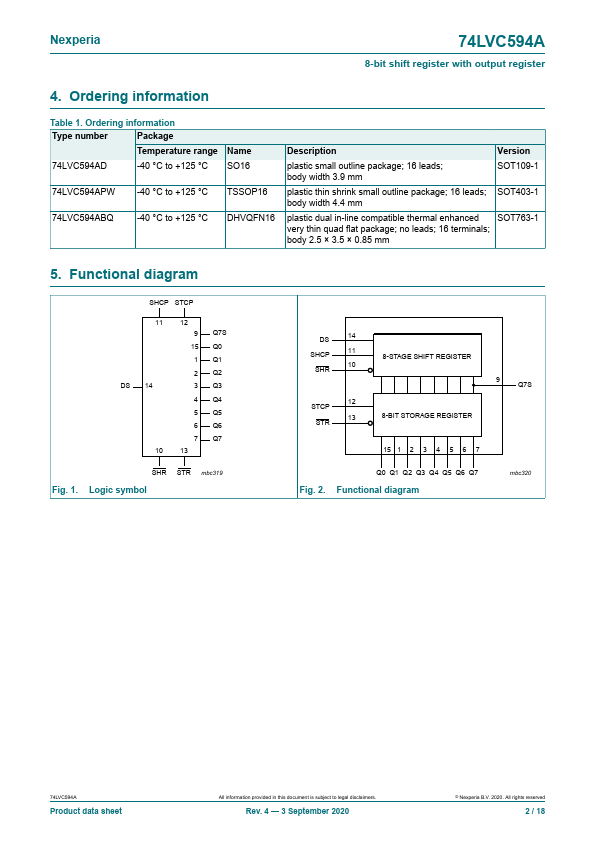

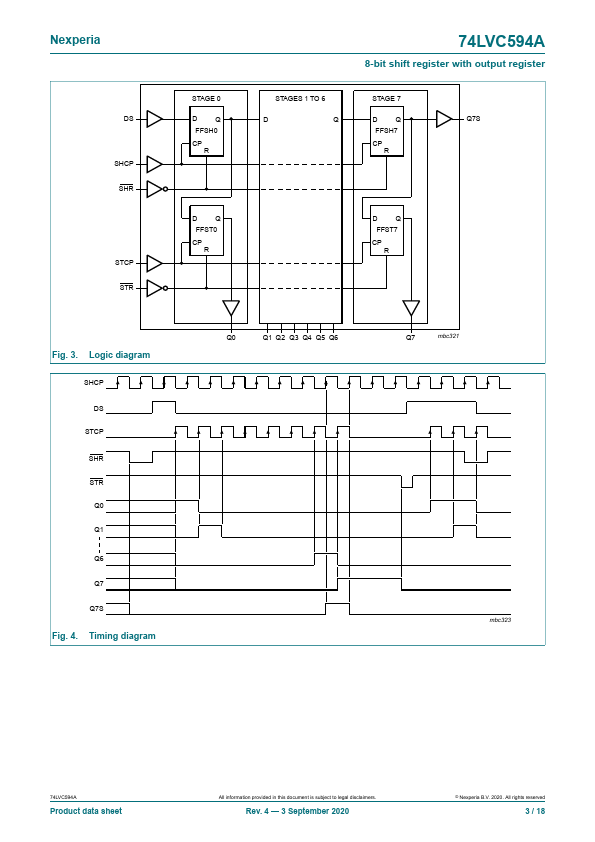

The 74LVC594A is an 8-bit serial-in/serial or parallel-out shift register with a storage register. Separate clock and reset inputs are provided on both shift and storage registers. The device Features a serial input (DS) and a serial output (Q7S) to enable cascading. Data is shifted on the LOW-to-HIGH transitions of the SHCP input, and the data in the shift register is transferred to the storage register on a LOW-to-HIGH transition of the STCP input. If both clocks are connected together, the shift register will always be one clock pulse ahead of the storage register. A...