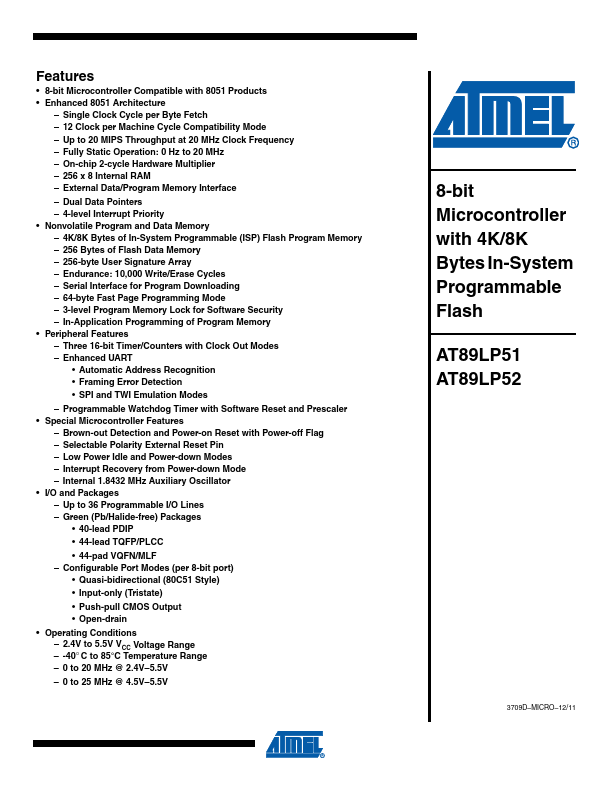

AT89LP52 Overview

Key Specifications

Package: PLCC

Mount Type: Surface Mount

Pins: 44

Max Voltage (typical range): 5.5 V

Key Features

- 8-bit Microcontroller Compatible with 8051 Products

- Peripheral Features – Three 16-bit Timer/Counters with Clock Out Modes – Enhanced UART

- Automatic Address Recognition

- Framing Error Detection

- SPI and TWI Emulation Modes – Programmable Watchdog Timer with Software Reset and Prescaler