AT89LP6440

Overview

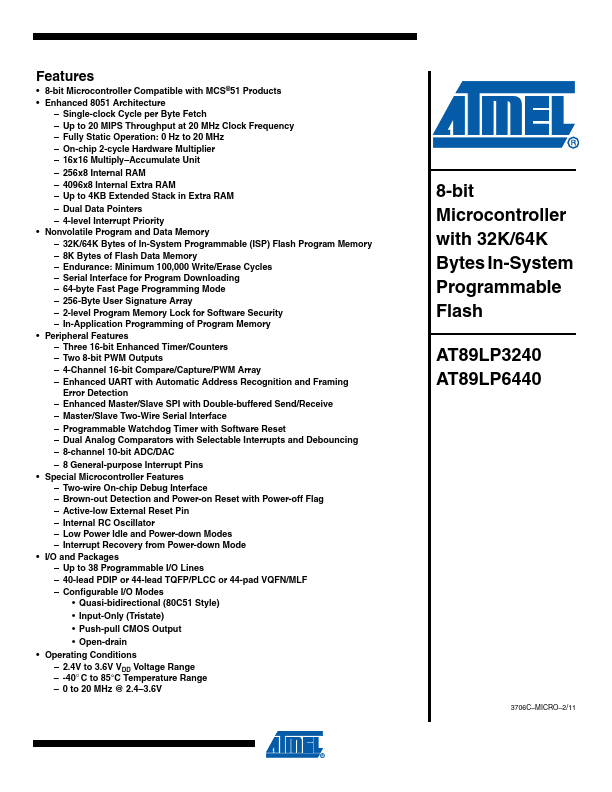

- 8-bit Microcontroller Compatible with MCS®51 Products

- Enhanced 8051 Architecture - Single-clock Cycle per Byte Fetch - Up to 20 MIPS Throughput at 20 MHz Clock Frequency - Fully Static Operation: 0 Hz to 20 MHz - On-chip 2-cycle Hardware Multiplier - 16x16 Multiply-Accumulate Unit - 256x8 Internal RAM - 4096x8 Internal Extra RAM - Up to 4KB Extended Stack in Extra RAM - Dual Data Pointers - 4-level Interrupt Priority

- Nonvolatile Program and Data Memory - 32K/64K Bytes of In-System Programmable (ISP) Flash Program Memory - 8K Bytes of Flash Data Memory - Endurance: Minimum 100,000 Write/Erase Cycles - Serial Interface for Program Downloading - 64-byte Fast Page Programming Mode - 256-Byte User Signature Array - 2-level Program Memory Lock for Software Security - In-Application Programming of Program Memory

- Peripheral Features - Three 16-bit Enhanced Timer/Counters - Two 8-bit PWM Outputs - 4-Channel 16-bit Compare/Capture/PWM Array - Enhanced UART with Automatic Address Recognition and Framing Error Detection - Enhanced Master/Slave SPI with Double-buffered Send/Receive - Master/Slave Two-Wire Serial Interface - Programmable Watchdog Timer with Software Reset - Dual Analog Comparators with Selectable Interrupts and Debouncing - 8-channel 10-bit ADC/DAC - 8 General-purpose Interrupt Pins

- Special Microcontroller Features - Two-wire On-chip Debug Interface - Brown-out Detection and Power-on Reset with Power-off Flag - Active-low External Reset Pin - Internal RC Oscillator - Low Power Idle and Power-down Modes - Interrupt Recovery from Power-down Mode

- I/O and Packages - Up to 38 Programmable I/O Lines - 40-lead PDIP or 44-lead TQFP/PLCC or 44-pad VQFN/MLF - Configurable I/O Modes

- Quasi-bidirectional (80C51 Style)

- Input-Only (Tristate)

- Push-pull CMOS Output

- Open-drain