90S1200 Overview

Description

The AT90S1200 is a low-power CMOS 8-bit microcontroller based on the AVR RISC architecture. By executing powerful instructions in a single clock cycle, the AT90S1200 achieves throughputs approaching 1 MIPS per MHz allowing the system designer to optimize power consumption versus processing speed.

Key Features

- Utilizes the AVR® RISC Architecture

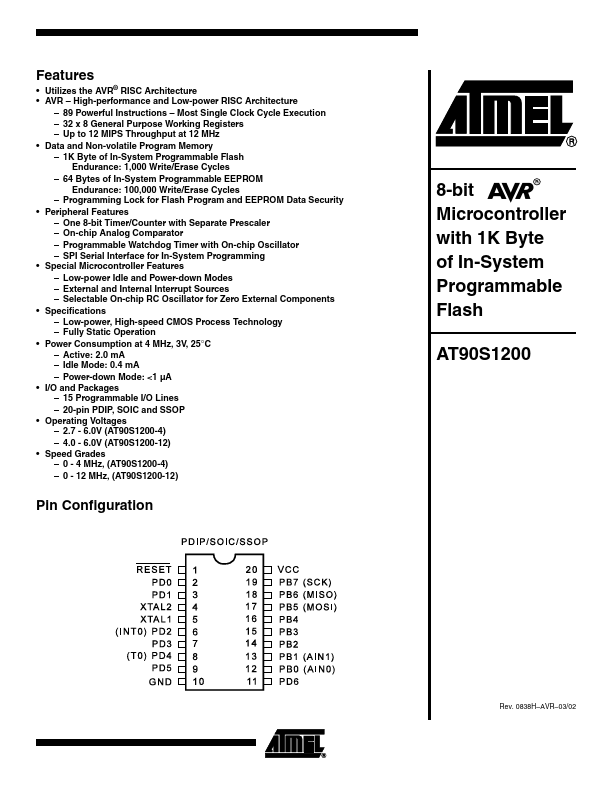

- 8-bit Microcontroller with 1K Byte of In-System Programmable Flash AT90S1200