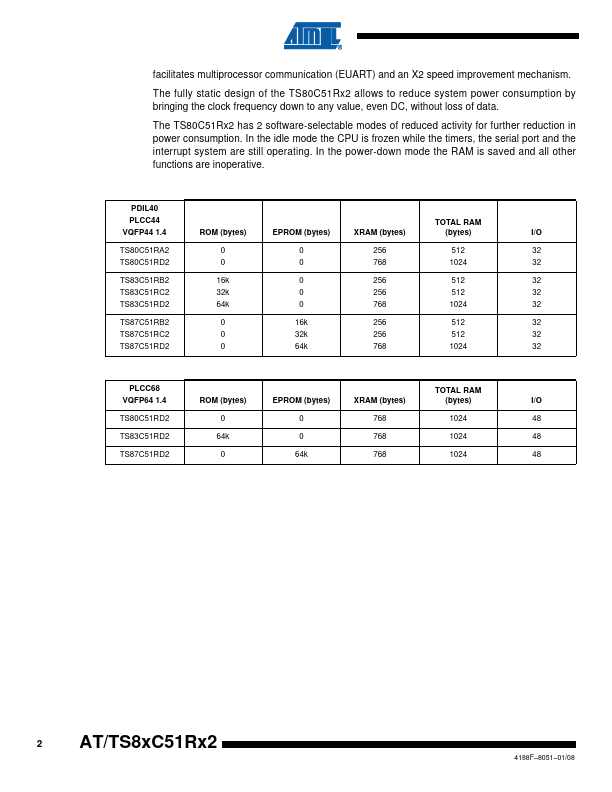

Datasheet Summary

1. Features

- 80C52 patible

- 8051 pin and instruction patible

- Four 8-bit I/O ports

- Three 16-bit timer/counters

- 256 bytes scratchpad RAM

- High-Speed Architecture

- 40 MHz @ 5V, 30MHz @ 3V

- X2 Speed Improvement capability (6 clocks/machine cycle)

- 30 MHz @ 5V, 20 MHz @ 3V (Equivalent to

- 60 MHz @ 5V, 40 MHz @ 3V)

- Dual Data Pointer

- On-chip ROM/EPROM (16K-bytes, 32K-bytes, 64K-bytes)

- On-chip eXpanded RAM (XRAM) (256 or 768 bytes)

- Programmable Clock Out and Up/Down Timer/Counter 2

- Programmable Counter Array with

- High Speed Output,

- pare / Capture,

- Pulse Width Modulator,

- Watchdog Timer Capabilities

- Hardware Watchdog Timer (One-time enabled with Reset-Out)

-...