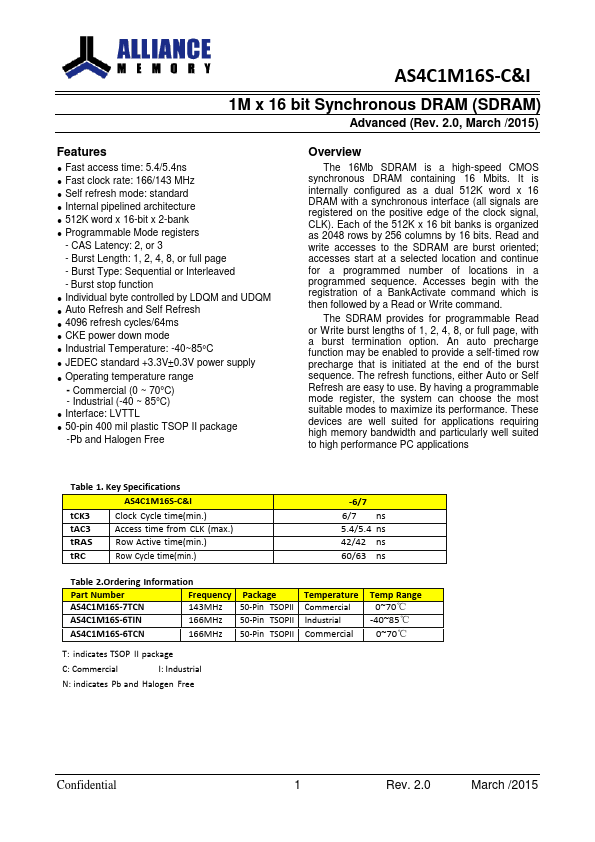

AS4C1M16S-I Description

Revision History Revision Rev 1.0 Rev 2.0 Details Preliminary datasheet Add 166MHZ and mercial & industrial parts. AS4C1M16S-C&I Date February 2015 March 2015 Alliance Memory Inc. 511 Taylor Way, San Carlos, CA 94070 TEL:.

AS4C1M16S-I Key Features

- Fast access time: 5.4/5.4ns

- Fast clock rate: 166/143 MHz

- Self refresh mode: standard

- Internal pipelined architecture

- 512K word x 16-bit x 2-bank

- Programmable Mode registers

- CAS Latency: 2, or 3

- Burst Length: 1, 2, 4, 8, or full page

- Burst Type: Sequential or Interleaved

- Burst stop function