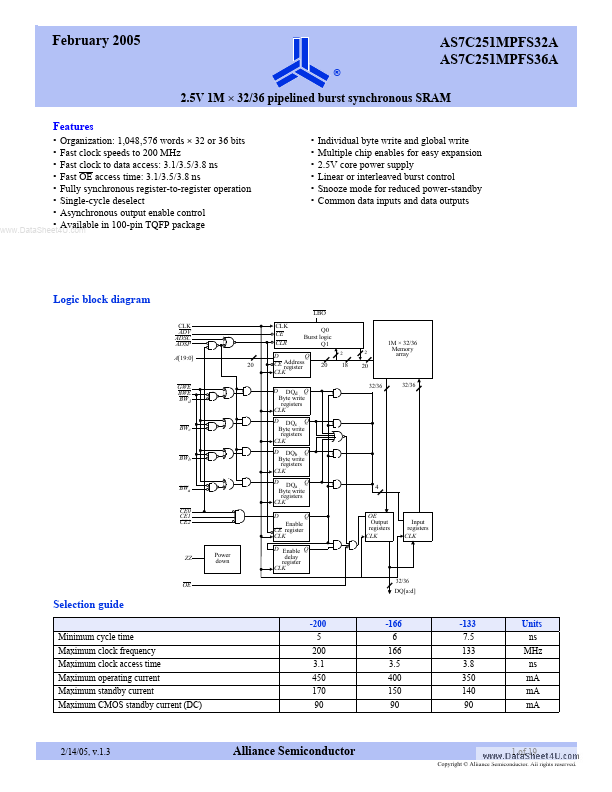

AS7C251MPFS36A Key Features

- Organization: 1,048,576 words × 32 or 36 bits

- Fast clock speeds to 200 MHz

- Fast clock to data access: 3.1/3.5/3.8 ns

- Fast OE access time: 3.1/3.5/3.8 ns

- Fully synchronous register-to-register operation

- Single-cycle deselect

- Asynchronous output enable control

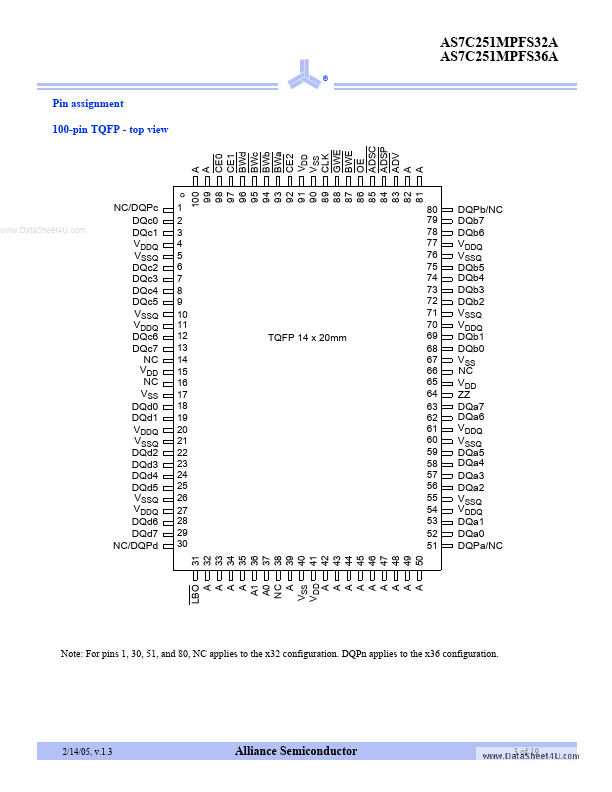

- Available in 100-pin TQFP package

- Individual byte write and global write Multiple chip enables for easy expansion 2.5V core power supply Linear or interle

- Single Cycle Deselect Pipelined Burst Synchronous SRAM