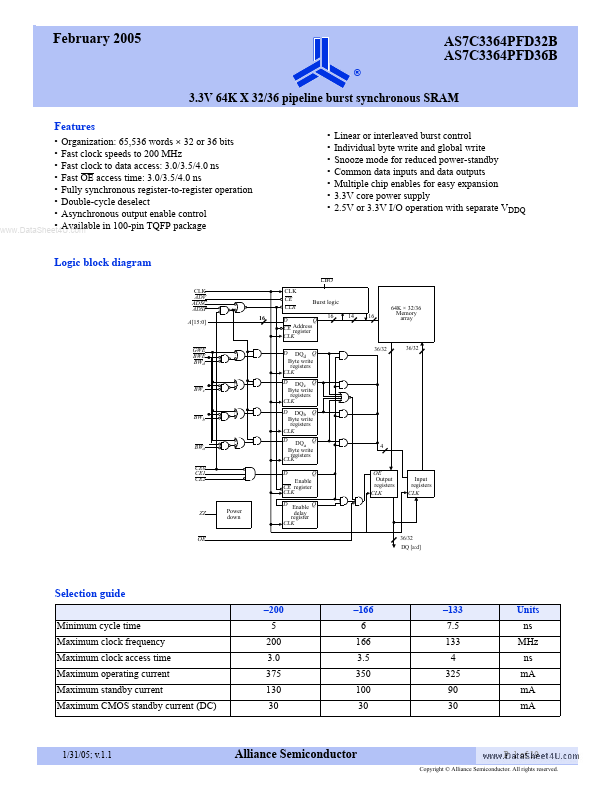

AS7C3364PFD36B Key Features

- Organization: 65,536 words × 32 or 36 bits

- Fast clock speeds to 200 MHz

- Fast clock to data access: 3.0/3.5/4.0 ns

- Fast OE access time: 3.0/3.5/4.0 ns

- Fully synchronous register-to-register operation

- Double-cycle deselect

- Asynchronous output enable control

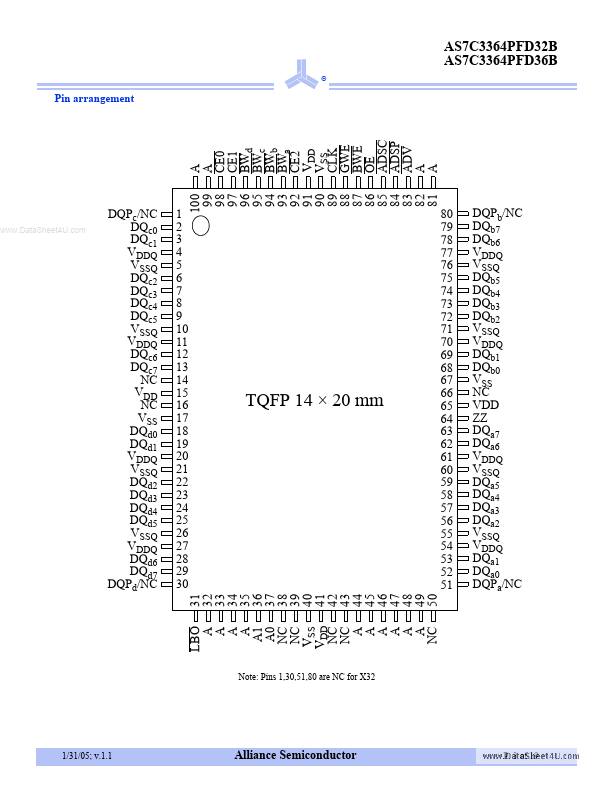

- Available in 100-pin TQFP package

- Linear or interleaved burst control Individual byte write and global write Snooze mode for reduced power-standby mon dat

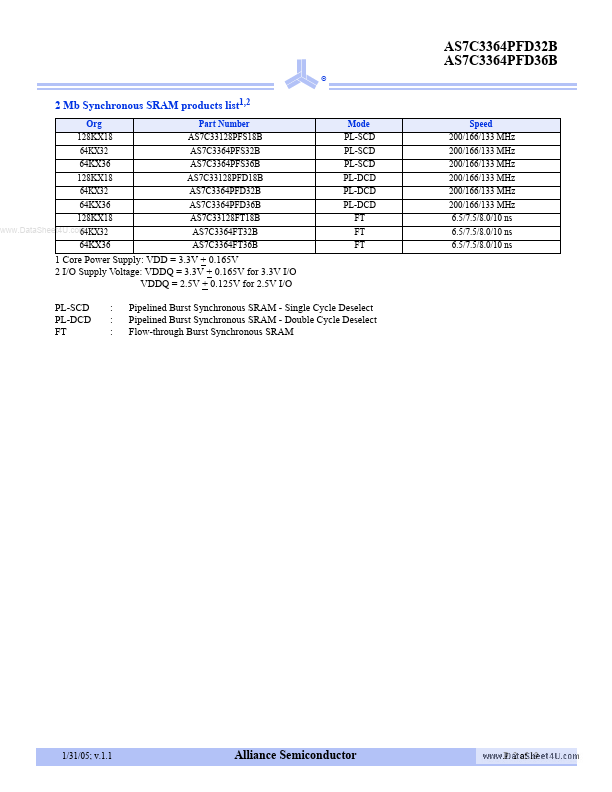

- Single Cycle Deselect Pipelined Burst Synchronous SRAM