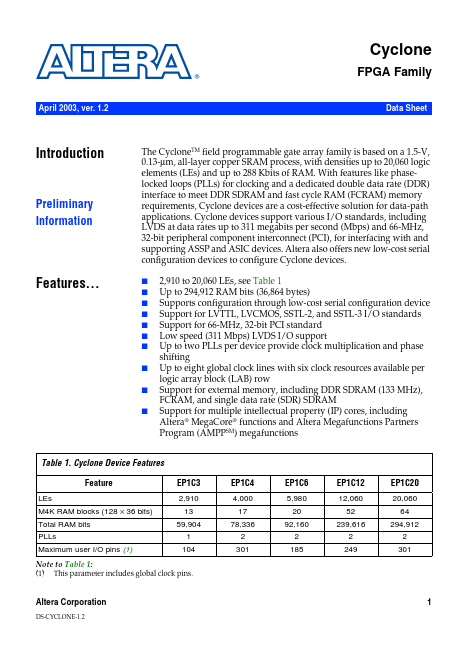

EP1C3

Overview

Preliminary Information.

- 2,910 to 20,060 LEs, see Table 1

- Up to 294,912 RAM bits (36,864 bytes)

- Supports configuration through low-cost serial configuration device

- Support for LVTTL, LVCMOS, SSTL-2, and SSTL-3 I/O standards

- Support for 66-MHz, 32-bit PCI standard

- Low speed (311 Mbps) LVDS I/O support

- Up to two PLLs per device provide clock multiplication and phase shifting

- Up to eight global clock lines with six clock resources available per logic array block (LAB) row

- Support for external memory, including DDR SDRAM (133 MHz), FCRAM, and single data rate (SDR) SDRAM

- Support for multiple intellectual property (IP) cores, including Altera MegaCore functions and Altera Megafunctions Partners Program (AMPPSM) megafunctions Table