EPF8820A

Overview

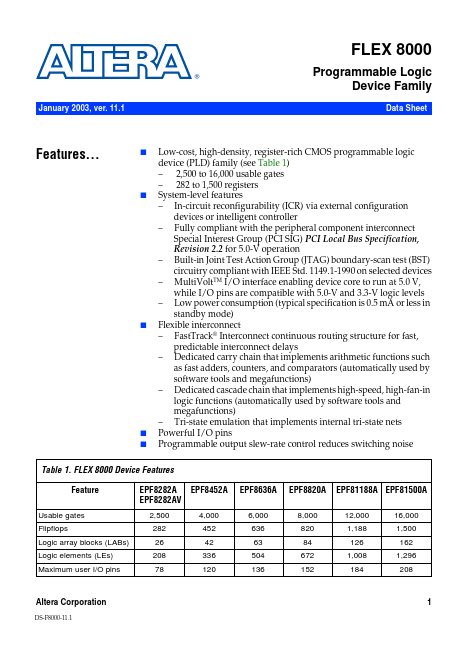

- Low-cost, high-density, register-rich CMOS programmable logic device (PLD) family (see Table 1) - 2,500 to 16,000 usable gates - 282 to 1,500 registers

- System-level features - In-circuit reconfigurability (ICR) via external configuration devices or intelligent controller - Fully compliant with the peripheral component interconnect Special Interest Group (PCI SIG) PCI Local Bus Specification, Revision 2.2 for 5.0-V operation - Built-in Joint Test Action Group (JTAG) boundary-scan test (BST) circuitry compliant with IEEE Std. 1149.1-1990 on selected devices - MultiVoltTM I/O interface enabling device core to run at 5.0 V, while I/O pins are compatible with 5.0-V and 3.3-V logic levels - Low power consumption (typical specification is 0.5 mA or less in standby mode)

- Flexible interconnect - FastTrack® Interconnect continuous routing structure for fast, predictable interconnect delays - Dedicated carry chain that implements arithmetic functions such as fast adders, counters, and comparators (automatically used by software tools and megafunctions) - Dedicated cascade chain that implements high-speed, high-fan-in logic functions (automatically used by software tools and megafunctions) - Tri-state emulation that implements internal tri-state nets

- Powerful I/O pins

- Programmable output slew-rate control reduces switching noise Table

- FLEX 8000 Device Features Feature