Datasheet Summary

..

®

Includes MAX 9000A

MAX 9000

Programmable Logic Device Family

Data Sheet

December 2002, ver. 6.4

Features

...

- -

- -

- -

- -

- -

- -

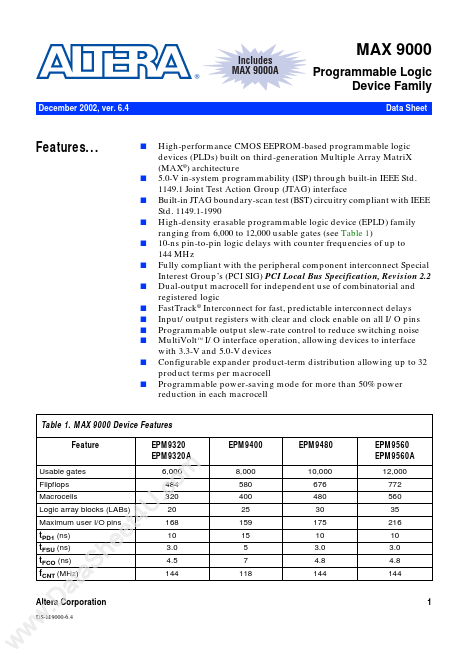

- High-performance CMOS EEPROM-based programmable logic devices (PLDs) built on third-generation Multiple Array MatriX (MAX®) architecture 5.0-V in-system programmability (ISP) through built-in IEEE Std. 1149.1 Joint Test Action Group (JTAG) interface Built-in JTAG boundary-scan test (BST) circuitry pliant with IEEE Std. 1149.1-1990 High-density erasable programmable logic device (EPLD) family ranging from 6,000 to 12,000 usable gates (see Table 1) 10-ns pin-to-pin logic delays with counter frequencies of up to 144 MHz Fully...