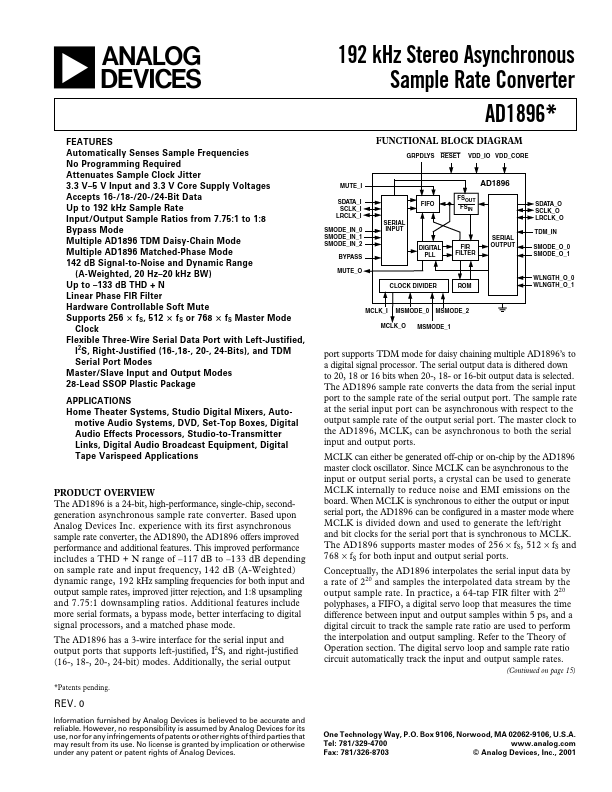

| Part | AD1896 |

|---|---|

| Description | 192 kHz Stereo Asynchronous Sample Rate Converter |

| Manufacturer | Analog Devices |

| Size | 1.27 MB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| B2405S-2W | MORNSUN | DUAL/SINGLE OUTPUT DC-DC CONVERTER |

| CN3903 | Chipnet | 36V/3.5A 500KHz Synchronous Step-Down Converter |

| MC34063 | STMicroelectronics | DC-DC CONVERTER CONTROLLER |