ADSP-21061L Description

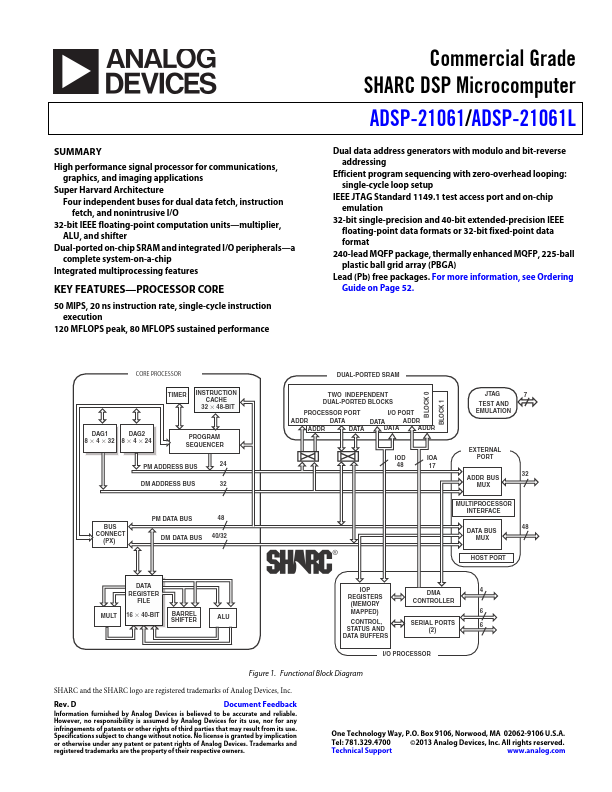

................................................. 3 SHARC Family Core Architecture ............................ 3 Memory and I/O Interface.

ADSP-21061L Key Features

- 1 Key Features-Processor Core

- 3 SHARC Family Core Architecture

- 3 Memory and I/O Interface Features

- 4 Porting Code From the ADSP-21060 or ADSP-21062