Datasheet Summary

SUMMARY

High performance 32-Bit DSP- applications in audio, medical, military, wireless munications, graphics, imaging, motor-control, and telephony

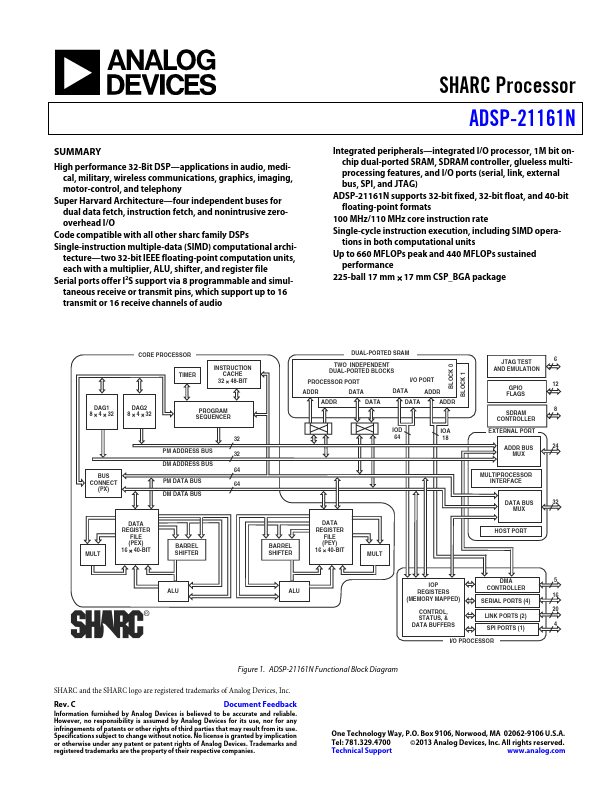

Super Harvard Architecture- four independent buses for dual data fetch, instruction fetch, and nonintrusive zerooverhead I/O

Code patible with all other sharc family DSPs Single-instruction multiple-data (SIMD) putational archi- tecture- two 32-bit IEEE floating-point putation units, each with a multiplier, ALU, shifter, and register file Serial ports offer I2S support via 8 programmable and simultaneous receive or transmit pins, which support up to 16 transmit or 16 receive channels of audio

SHARC Processor

Integrated...