Datasheet Summary

SUMMARY

High performance 32-bit DSP- applications in audio, medical, military, graphics, imaging, and munication

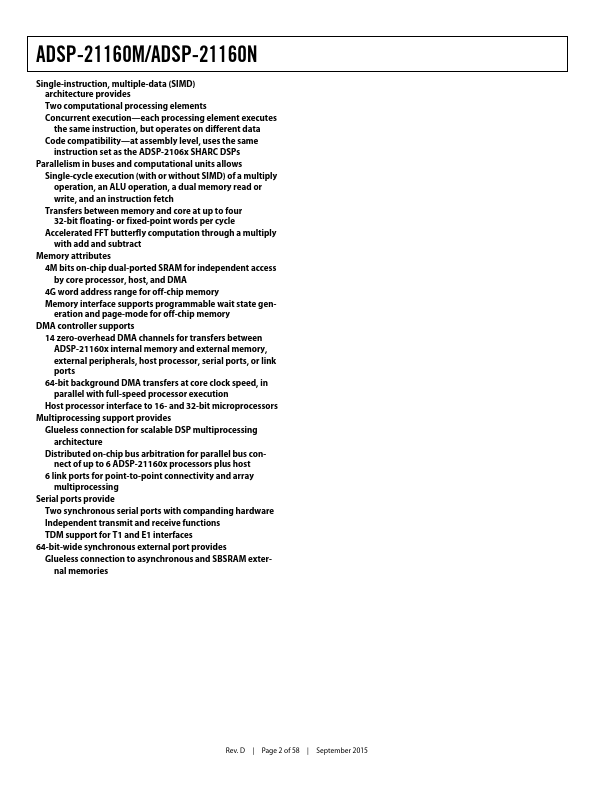

Super Harvard architecture- 4 independent buses for dual data fetch, instruction fetch, and nonintrusive, zero-overhead I/O

Backward patible- assembly source level patible with code for ADSP-2106x DSPs

Single-instruction, multiple-data (SIMD) putational architecture- two 32-bit IEEE floating-point putation units, each with a multiplier, ALU, shifter, and register file

Integrated peripherals- integrated I/O processor, 4M bits on-chip dual-ported SRAM, glueless multiprocessing Features

, and ports (serial, link, external bus, and JTAG)

SHARC

Digital Signal Processor

ADSP-2...