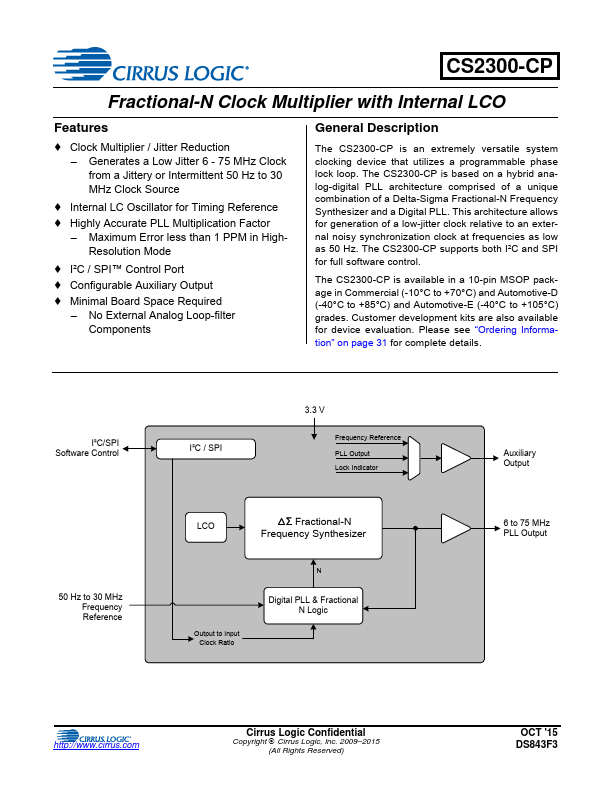

CS2300-CP Description

The CS2300-CP is an extremely versatile system clocking device that utilizes a programmable phase lock loop. The CS2300-CP is based on a hybrid analog-digital PLL architecture prised of a unique bination of a Delta-Sigma Fractional-N Frequency Synthesizer and a Digital PLL. This architecture allows for generation of a low-jitter clock relative to an external noisy synchronization clock at frequencies as low as 50 Hz.

CS2300-CP Key Features

- Generates a Low Jitter 6

- 75 MHz Clock from a Jittery or Intermittent 50 Hz to 30 MHz Clock Source

- Maximum Error less than 1 PPM in HighResolution Mode

- No External Analog Loop-filter ponents