CS2300-01

CS2300-01 is Clock Multiplier manufactured by Cirrus Logic.

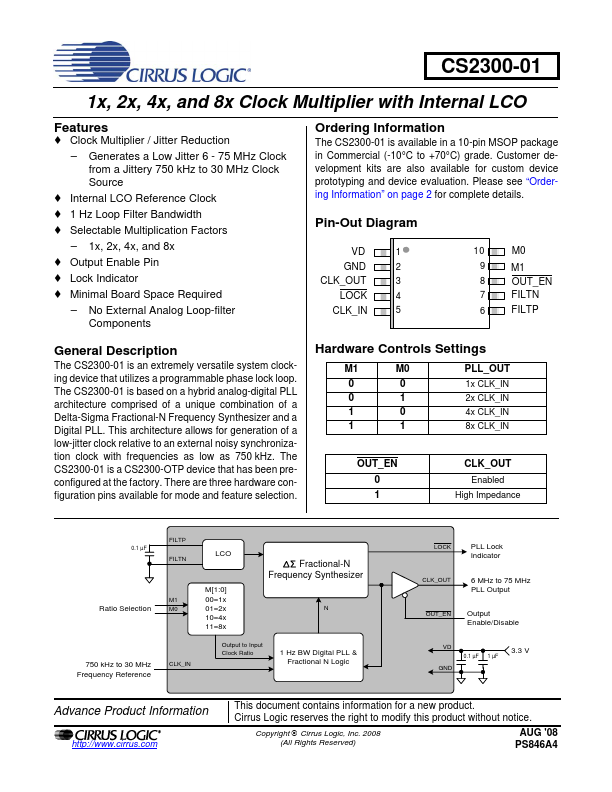

Features

Clock Multiplier / Jitter Reduction

- Generates a Low Jitter 6

- 75 MHz Clock from a Jittery 750 k Hz to 30 MHz Clock Source

Internal LCO Reference Clock 1 Hz Loop Filter Bandwidth Selectable Multiplication Factors

- 1x, 2x, 4x, and 8x Output Enable Pin Lock Indicator Minimal Board Space Required

- No External Analog Loop-filter ponents

Ordering Information

The CS2300-01 is available in a 10-pin MSOP package in mercial (-10°C to +70°C) grade. Customer development kits are also available for custom device prototyping and device evaluation. Please see “Ordering Information” on page 2 for plete details.

Pin-Out Diagram

CLK_OUT

LOCK

CLK_IN

M0

M1

OUT_EN

FILTN

FILTP

General Description

The CS2300-01 is an extremely versatile system clocking device that utilizes a programmable phase lock loop. The CS2300-01 is based on a hybrid analog-digital PLL architecture prised of a unique bination of a Delta-Sigma Fractional-N Frequency Synthesizer and a Digital PLL. This architecture allows for generation of a low-jitter clock relative to an external noisy synchronization clock with frequencies as low as 750 k Hz. The CS2300-01 is a CS2300-OTP device that has been preconfigured at the factory. There are three hardware configuration pins available for mode and feature selection.

Hardware Controls...