CY9BF524M

Overview

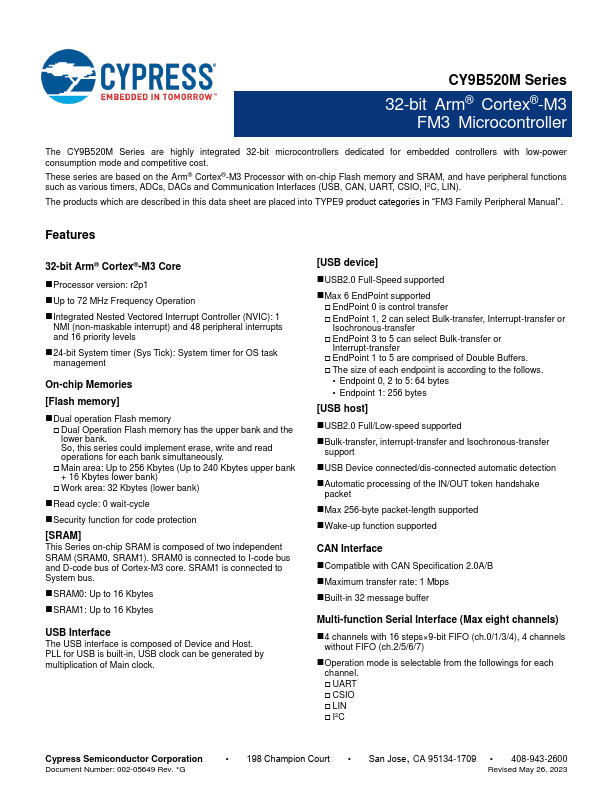

- Processor version: r2p1

- Up to 72 MHz Frequency Operation

- Integrated Nested Vectored Interrupt Controller (NVIC): 1 NMI (non-maskable interrupt) and 48 peripheral interrupts and 16 priority levels

- 24-bit System timer (Sys Tick): System timer for OS task management On-chip Memories [Flash memory]

- Dual operation Flash memory Dual Operation Flash memory has the upper bank and the lower bank. So, this series could implement erase, write and read operations for each bank simultaneously. Main area: Up to 256 Kbytes (Up to 240 Kbytes upper bank + 16 Kbytes lower bank) Work area: 32 Kbytes (lower bank)

- Read cycle: 0 wait-cycle

- Security function for code protection [SRAM] This Series on-chip SRAM is composed of two independent SRAM (SRAM0, SRAM1). SRAM0 is connected to I-code bus and D-code bus of Cortex-M3 core. SRAM1 is connected to System bus.

- SRAM0: Up to 16 Kbytes

- SRAM1: Up to 16 Kbytes USB Interface The USB interface is composed of Device and Host. PLL for USB is built-in, USB clock can be generated by multiplication of Main clock. [USB device]

- USB2.0 Full-Speed supported