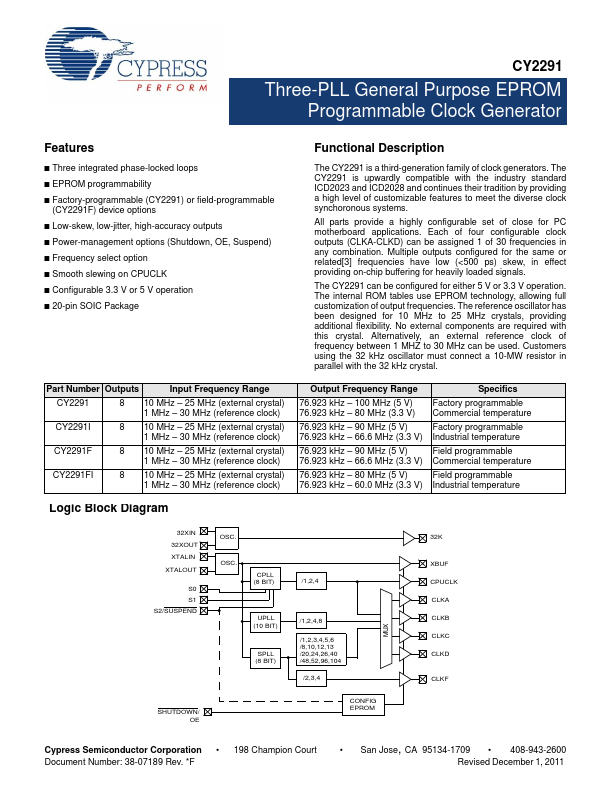

CY2291 Description

The CY2291 is a third-generation family of clock generators. The CY2291 is upwardly patible with the industry standard ICD2023 and ICD2028 and continues their tradition by providing a high level of customizable.

CY2291 Key Features

- Three integrated phase-locked loops

- EPROM programmability

- Factory-programmable (CY2291) or field-programmable

- Low-skew, low-jitter, high-accuracy outputs

- Power-management options (Shutdown, OE, Suspend)

- Frequency select option

- Smooth slewing on CPUCLK

- Configurable 3.3 V or 5 V operation

- 20-pin SOIC Package