CY2PP326 Description

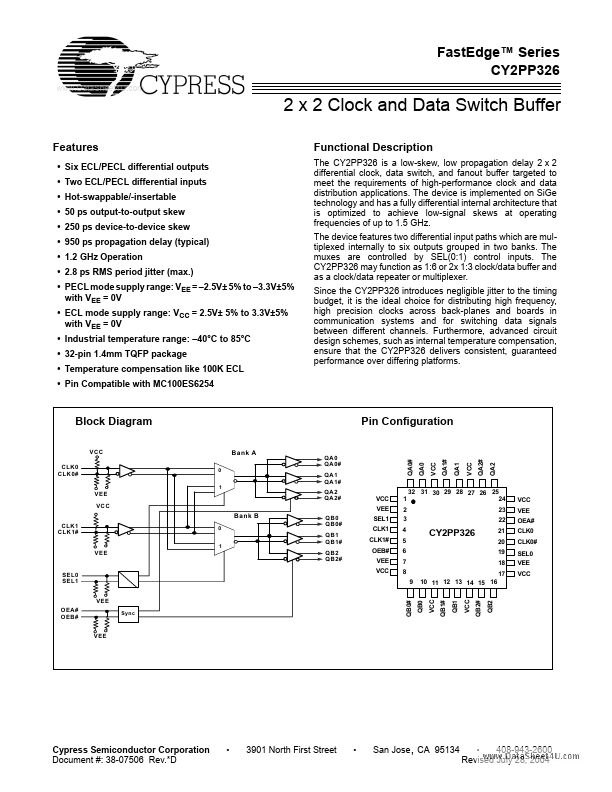

The CY2PP326 is a low-skew, low propagation delay 2 x 2 differential clock, data switch, and fanout buffer targeted to meet the requirements of high-performance clock and data distribution applications. The device is implemented on SiGe technology and has a fully differential internal architecture that is optimized to achieve low-signal skews at operating frequencies of up to 1.5 GHz.

CY2PP326 Key Features

- Six ECL/PECL differential outputs

- Two ECL/PECL differential inputs

- Hot-swappable/-insertable

- 50 ps output-to-output skew

- 250 ps device-to-device skew

- 950 ps propagation delay (typical)

- 1.2 GHz Operation

- 2.8 ps RMS period jitter (max.)

- PECL mode supply range: VEE = -2.5V± 5% to -3.3V±5% with VEE = 0V

- ECL mode supply range: VCC = 2.5V± 5% to 3.3V±5% with VEE = 0V