CY7C1312KV18

CY7C1312KV18 is 18-Mbit QDR II SRAM Two-Word Burst Architecture manufactured by Cypress.

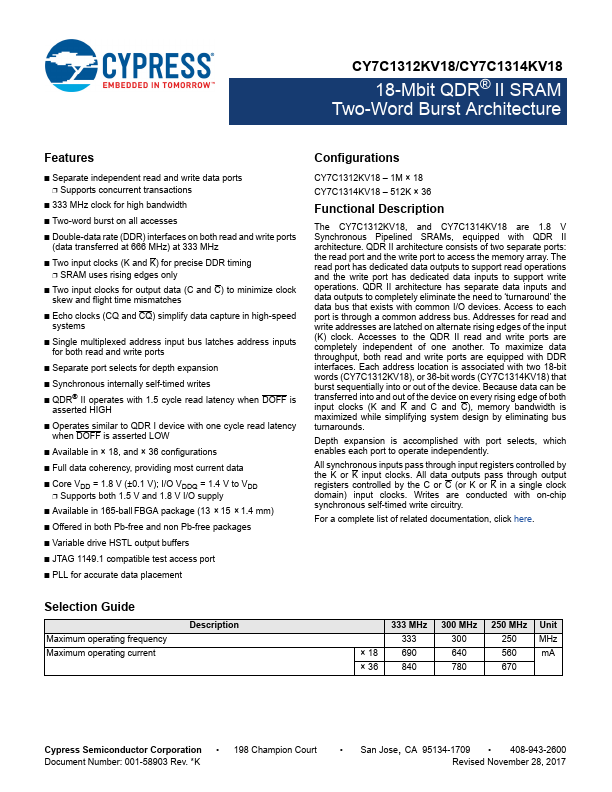

CY7C1312KV18/CY7C1314KV18

18-Mbit QDR® II SRAM Two-Word Burst Architecture

18-Mbit QDR® II SRAM Two-Word Burst Architecture

Features

- Separate independent read and write data ports

- Supports concurrent transactions

- 333 MHz clock for high bandwidth

- Two-word burst on all accesses

- Double-data rate (DDR) interfaces on both read and write ports

(data transferred at 666 MHz) at 333 MHz

- Two input clocks (K and K) for precise DDR timing

- SRAM uses rising edges only

- Two input clocks for output data (C and C) to minimize clock skew and flight time mismatches

- Echo clocks (CQ and CQ) simplify data capture in high-speed systems

- Single multiplexed address input bus latches address inputs for both read and write ports

- Separate port selects for depth expansion

- Synchronous internally self-timed writes

- QDR® II operates with 1.5 cycle read latency when DOFF is asserted HIGH

- Operates similar to QDR I device with one cycle read latency when DOFF is asserted LOW

- Available in × 18, and × 36 configurations

- Full data coherency, providing most current data

- Core VDD = 1.8 V (±0.1 V); I/O VDDQ = 1.4 V to VDD

- Supports both 1.5 V and 1.8 V I/O supply

- Available in 165-ball FBGA package (13 × 15 × 1.4 mm)

- Offered in both Pb-free and non Pb-free packages

- Variable drive HSTL output buffers

- JTAG 1149.1 patible test access port

- PLL for accurate data placement

Configurations

- 1M × 18...