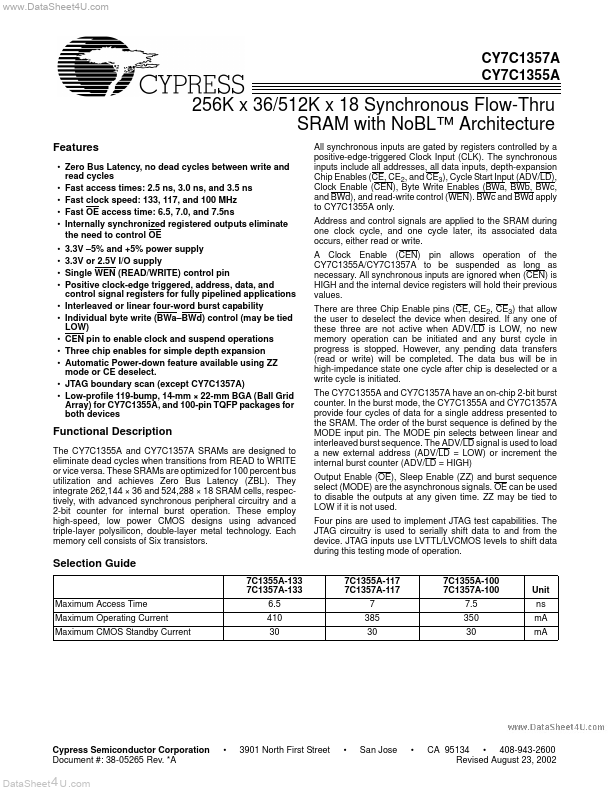

CY7C1355A Overview

Key Specifications

Package: TQFP

Mount Type: Surface Mount

Pins: 100

Operating Voltage: 3.3 V

Key Features

- Zero Bus Latency, no dead cycles between write and read cycles

- Fast access times: 2.5 ns, 3.0 ns, and 3.5 ns

- Fast clock speed: 133, 117, and 100 MHz

- Fast OE access time: 6.5, 7.0, and 7.5ns

- Internally synchronized registered outputs eliminate the need to control OE