CY7C1482BV25 Description

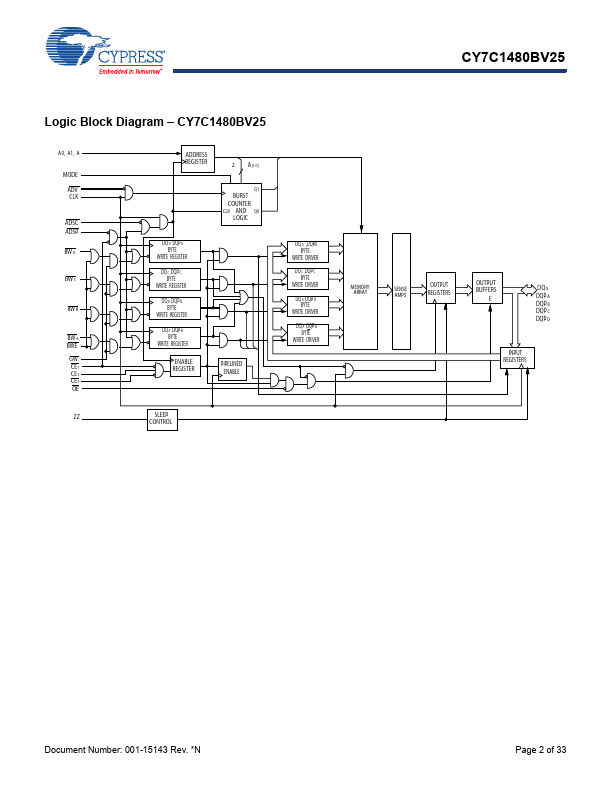

All synchronous inputs are gated by registers controlled by a positive-edge-triggered Clock Input (CLK). The synchronous inputs include all addresses, all data inputs, address-pipelining Chip Enable (CE1), depth-expansion Chip Enables (CE2 and CE3), Burst Control inputs (ADSC, ADSP, and ADV), Write Enables (BWX, and BWE), and Global Write (GW). Asynchronous inputs include the Output Enable (OE) and the ZZ pin.

CY7C1482BV25 Key Features

- Functional Description

- Selection Guide

- 198 Champion Court

- San Jose, CA 95134-1709

- 408-943-2600 Revised February 29, 2008

- CY7C1480BV25 (2M x 36)