CY7C1670KV18

CY7C1670KV18 is 144-Mbit DDR II+ SRAM Two-Word Burst Architecture manufactured by Cypress.

- Part of the CY7C1668KV18 comparator family.

- Part of the CY7C1668KV18 comparator family.

CY7C1668KV18 CY7C1670KV18

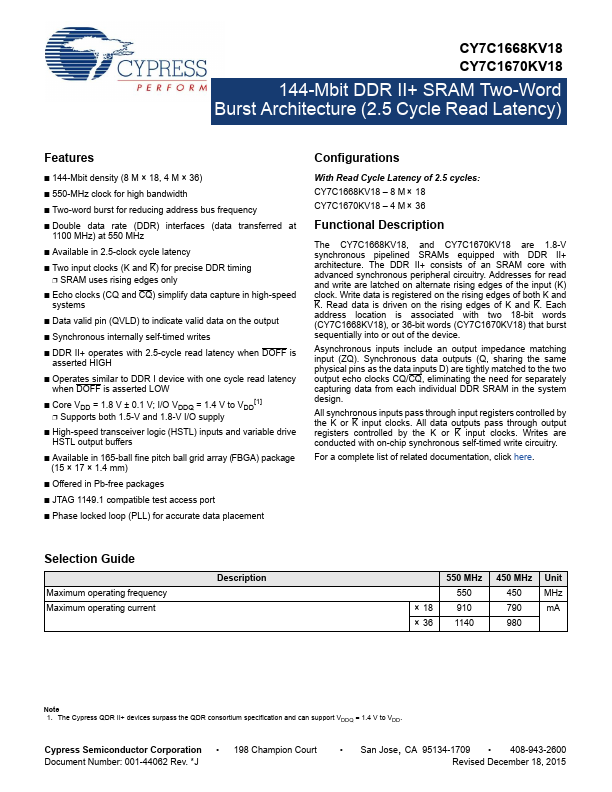

144-Mbit DDR II+ SRAM Two-Word Burst Architecture (2.5 Cycle Read Latency)

144-Mbit DDR II+ SRAM Two-Word Burst Architecture (2.5 Cycle Read Latency)

Features

- 144-Mbit density (8 M × 18, 4 M × 36)

- 550-MHz clock for high bandwidth

- Two-word burst for reducing address bus frequency

- Double data rate (DDR) interfaces (data transferred at

1100 MHz) at 550 MHz

- Available in 2.5-clock cycle latency

- Two input clocks (K and K) for precise DDR timing

- SRAM uses rising edges only

- Echo clocks (CQ and CQ) simplify data capture in high-speed systems

- Data valid pin (QVLD) to indicate valid data on the output

- Synchronous internally self-timed writes

- DDR II+ operates with 2.5-cycle read latency when DOFF is asserted HIGH

- Operates similar to DDR I device with one cycle read latency when DOFF is asserted LOW

- Core VDD = 1.8 V ± 0.1 V; I/O VDDQ = 1.4 V to VDD[1]

- Supports both 1.5-V and 1.8-V I/O supply

- High-speed...