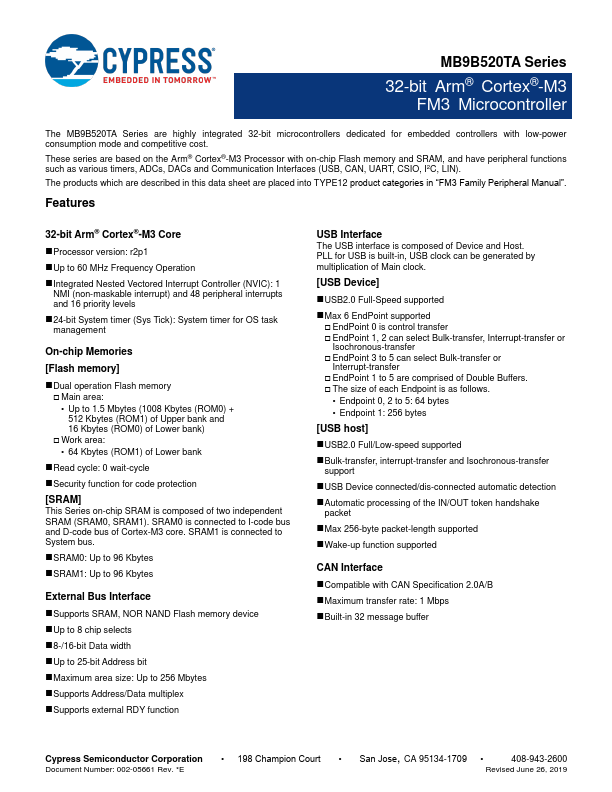

MB9B520TA

MB9B520TA is 32-bit Microcontroller manufactured by Cypress.

32-bit Arm® Cortex®-M3 Core

- Processor version: r2p1

- Up to 60 MHz Frequency Operation

- Integrated Nested Vectored Interrupt Controller (NVIC): 1

NMI (non-maskable interrupt) and 48 peripheral interrupts and 16 priority levels

- 24-bit System timer (Sys Tick): System timer for OS task management

On-chip Memories

[Flash memory]

- Dual operation Flash memory

Main area:

- Up to 1.5 Mbytes (1008 Kbytes (ROM0) + 512 Kbytes (ROM1) of Upper bank and 16 Kbytes (ROM0) of Lower bank)

Work area:

- 64 Kbytes (ROM1) of Lower bank

- Read cycle: 0 wait-cycle

- Security function for code protection

[SRAM]

This Series on-chip SRAM is posed of two independent SRAM (SRAM0, SRAM1). SRAM0 is connected to I-code bus and D-code bus of Cortex-M3 core. SRAM1 is connected to System bus.

- SRAM0: Up to 96 Kbytes

- SRAM1: Up to 96 Kbytes

External Bus Interface

- Supports SRAM, NOR NAND Flash memory device

- Up to 8 chip selects

- 8-/16-bit Data width

- Up to 25-bit Address bit

- Maximum area size: Up to 256 Mbytes

- Supports Address/Data multiplex

- Supports external RDY function

USB Interface

The USB interface is posed of Device and Host. PLL for USB is built-in, USB clock can be generated by multiplication of Main...