Datasheet Summary

1P AL CE 20 V8 fax id: 6010

PALCE20V8

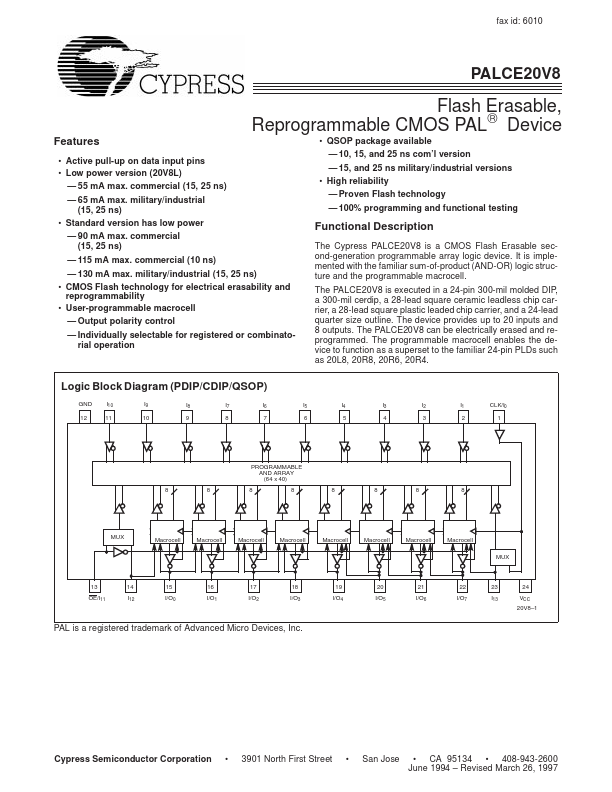

Flash Erasable, Reprogrammable CMOS PAL® Device

Features

- Active pull-up on data input pins

- Low power version (20V8L)

- 55 mA max. mercial (15, 25 ns)

- 65 mA max. military/industrial (15, 25 ns)

- Standard version has low power

- 90 mA max. mercial (15, 25 ns)

- 115 mA max. mercial (10 ns)

- 130 mA max. military/industrial (15, 25 ns)

- CMOS Flash technology for electrical erasability and reprogrammability

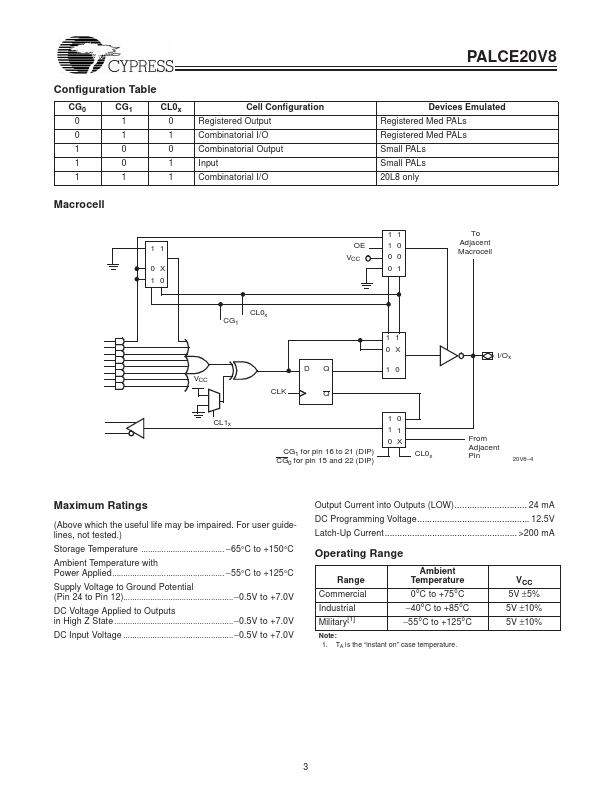

- User-programmable macrocell

- Output polarity control

- Individually selectable for registered or binatorial operation

- QSOP package available

- 10, 15, and 25 ns ’l version

- 15, and 25 ns military/industrial versions

- High...