M55D4G32128A-EEBG2R

M55D4G32128A-EEBG2R is 16M x 32 Bit x 8 Banks LPDDR3 SDRAM manufactured by Elite Semiconductor Microelectronics Technology.

- Part of the M55D4G32128A-GFBG2R comparator family.

- Part of the M55D4G32128A-GFBG2R comparator family.

Feature

- Ultra-low-voltage core and I/O power supplies VDD1 = 1.70- 1.95V VDD2, VDDCA, VDDQ = 1.14- 1.30V

- Organization 16M words x 32 bits x 8 banks

- JEDEC LPDDR3-pliant

- 4KB page size

Row address: R0 to R13 Column address: C0 to C9 (x32 bits)

- Auto precharge option for each burst access

- Eight-bit prefetch DDR architecture

- Eight internal banks for concurrent operation

- Double data rate, mand/address inputs; mands entered on each CK edge

- Bidirectional/differential data strobe per byte of data (DQS)

- Differential clock inputs (CK_t and CK_c)

- Data mask (DM) for write data

M55D4G32128A (2R)

16M x 32 Bit x 8 Banks LPDDR3 SDRAM

- mand/Address (CA) training for CA input timing adjustment

- Write leveling for clock to DQ, DQS, and DM timing adjustment

- Interface: HSUL_12

- Read latency (RL): 3, 6, 8, 9, 10, 11, 12, 14, 16

- Burst length (BL): 8

- Burst type (BT): Sequential

- Per-bank refresh for concurrent operation

- Auto temperature pensated self refresh (ATCSR)

- Auto refresh and self refresh

- Refresh cycles: 8192 cycles/32ms

Average refresh period: 3.9μs

- Partial-array self refresh (PASR)

Bank masking Segment masking

- Deep power-down (DPD)

- Programmable drive strength (DS)

- On-die termination (ODT)

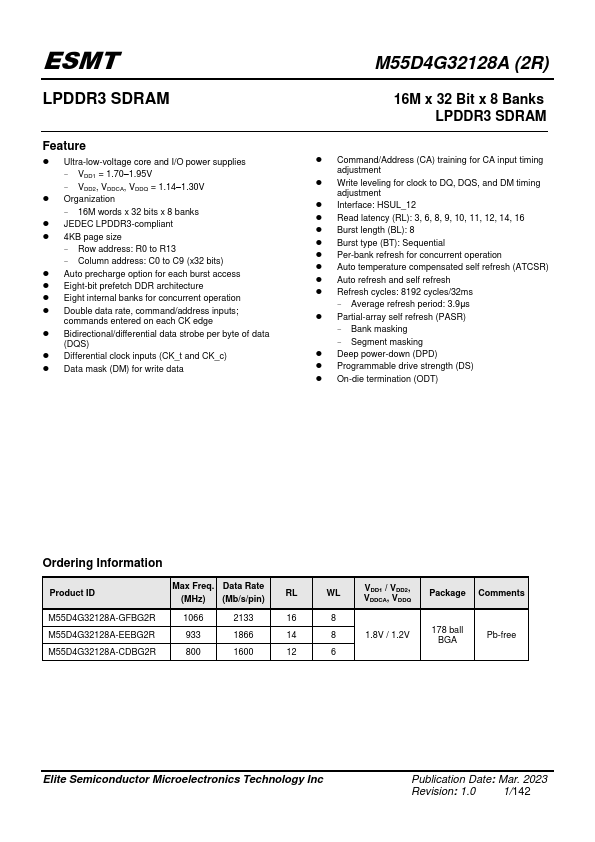

Ordering Information

Product ID

Max Freq. Data Rate RL

(MHz) (Mb/s/pin)

M55D4G32128A-GFBG2R

M55D4G32128A-CDBG2R

VDD1 / VDD2, VDDCA, VDDQ

Package...