EBE41RE4AAHA Overview

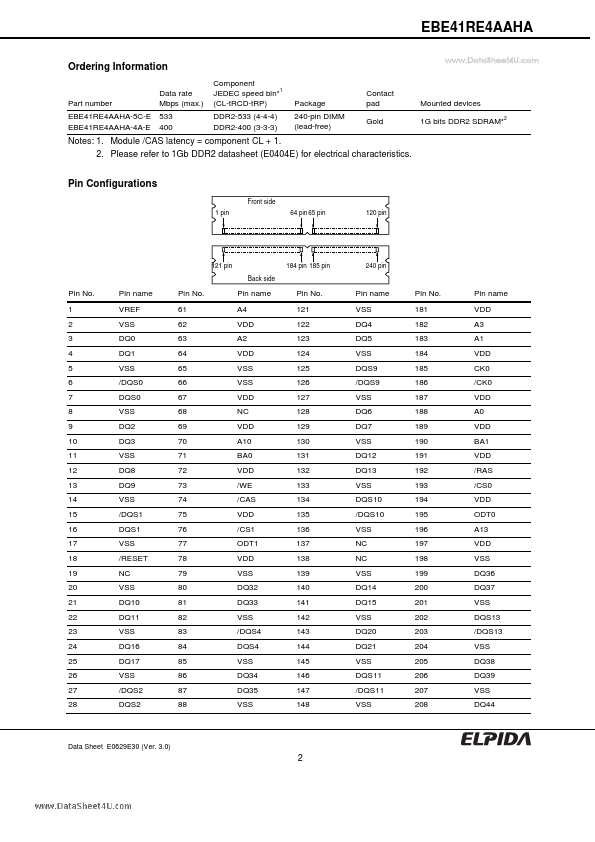

4GB Registered DDR2 SDRAM DIMM EBE41RE4AAHA (512M words × 72 bits, 2 Ranks) Specifications Density: 4GB Organization ⎯ 512M words × 72 bits, 2 ranks Mounting 36 pieces of 1G bits DDR2 SDRAM with sFBGA Package: 240-pin socket type dual in line memory module (DIMM) ⎯ PCB height:.

EBE41RE4AAHA Key Features

- Double-data-rate architecture; two data transfers per clock cycle

- The high-speed data transfer is realized by the 4 bits prefetch pipelined architecture

- Bi-directional differential data strobe (DQS and /DQS) is transmitted/received with data for capturing data at the recei

- DQS is edge-aligned with data for READs; centeraligned with data for WRITEs

- Differential clock inputs (CK and /CK)

- DLL aligns DQ and DQS transitions with CK transitions

- mands entered on each positive CK edge; data referenced to both edges of DQS

- Posted /CAS by programmable additive latency for better mand and data bus efficiency

- Off-Chip-Driver Impedance Adjustment and On-DieTermination for better signal quality

- /DQS can be disabled for single-ended Data Strobe operation