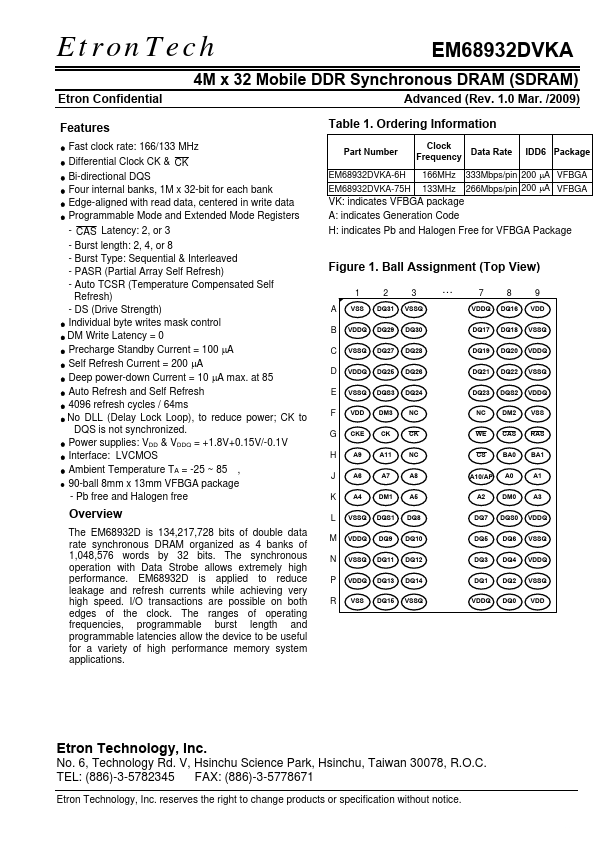

EM68932DVKA Description

.DataSheet.co.kr EtronTech Etron Confidential.

EM68932DVKA Key Features

- CAS Latency: 2, or 3

- Burst length: 2, 4, or 8

- Burst Type: Sequential & Interleaved

- PASR (Partial Array Self Refresh)

- Auto TCSR (Temperature pensated Self Refresh)

- DS (Drive Strength)

- Individual byte writes mask control

- DM Write Latency = 0

- Precharge Standby Current = 100 µA

- Self Refresh Current = 200 µA