MCZ33689D Description

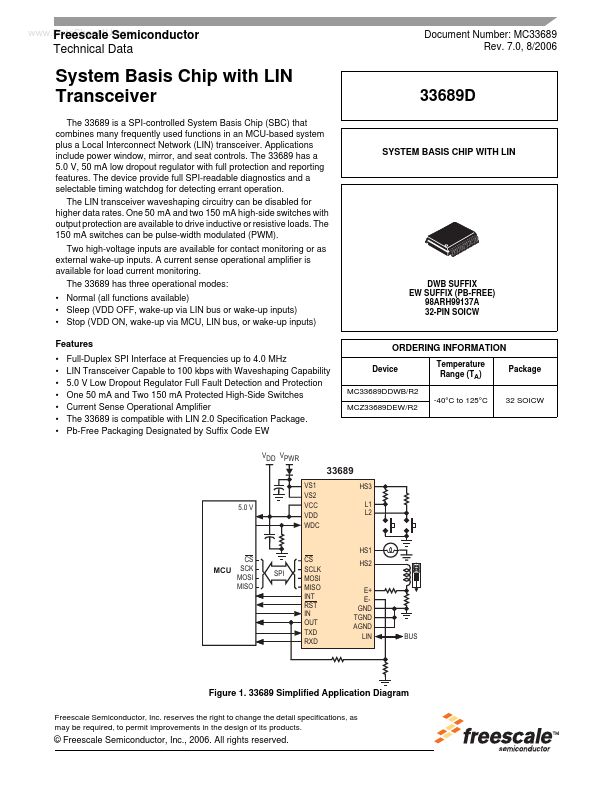

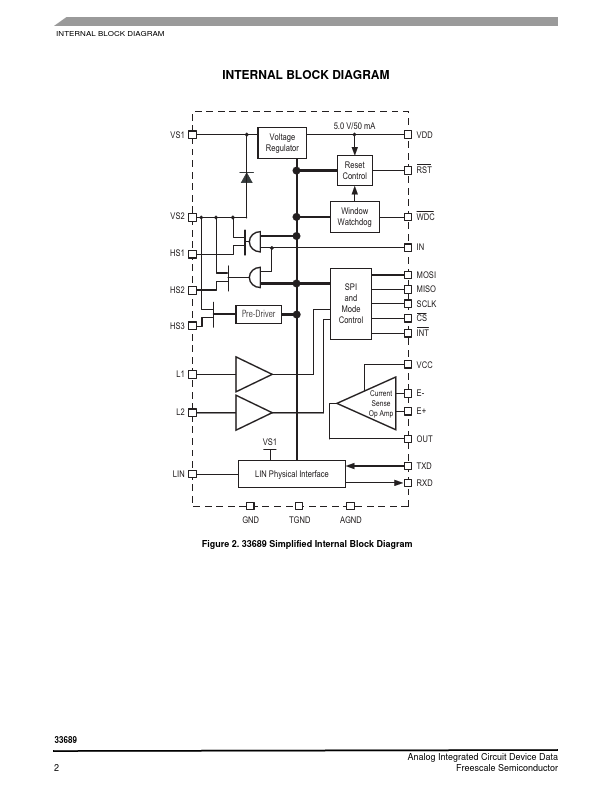

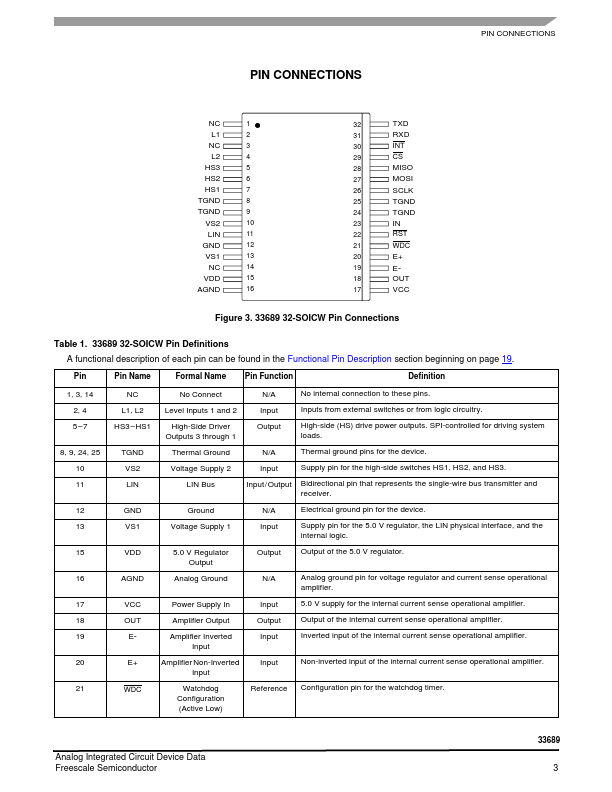

Freescale Semiconductor Technical Data Document Number: 7.0, 8/2006 System Basis Chip with LIN Transceiver The 33689 is a SPI-controlled System Basis Chip (SBC) that bines many frequently used functions in an MCU-based system plus a Local Interconnect Network (LIN) transceiver. Applications include power window, mirror, and seat controls.

MCZ33689D Key Features

- Normal (all functions available)

- Sleep (VDD OFF, wake-up via LIN bus or wake-up inputs)

- Stop (VDD ON, wake-up via MCU, LIN bus, or wake-up inputs) Features

- Full-Duplex SPI Interface at Frequencies up to 4.0 MHz LIN Transceiver Capable to 100 kbps with Waveshaping Capability 5

MCZ33689D Applications

- Normal (all functions available)