HMS1M32Z8A Key Features

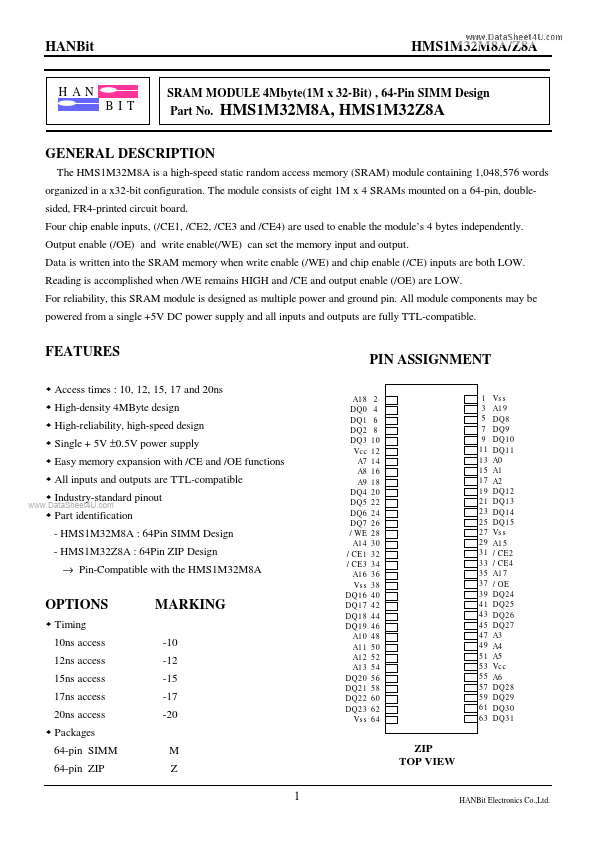

- Access times : 10, 12, 15, 17 and 20ns

- High-density 4MByte design

- High-reliability, high-speed design

- Single + 5V ±0.5V power supply

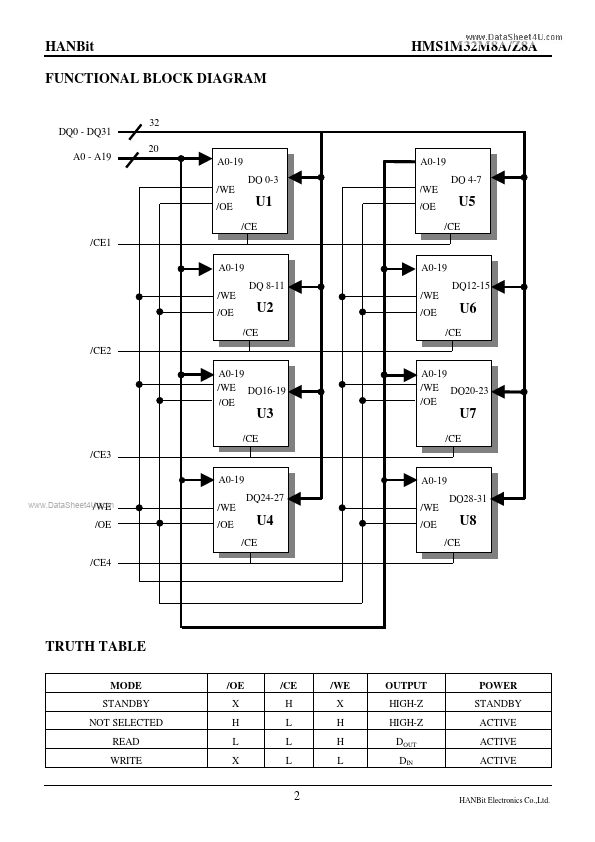

- Easy memory expansion with /CE and /OE functions

- All inputs and outputs are TTL-patible

- Industry-standard pinout

- Part identification

- HMS1M32M8A : 64Pin SIMM Design

- HMS1M32Z8A : 64Pin ZIP Design → Pin-patible with the HMS1M32M8A