Datasheet Summary

..

Agilent HDMP-0422 Single Port Bypass Circuit with CDR & Data Valid Detection Capability for Fibre Channel Arbitrated Loops Data Sheet

Features

- Supports 1.0625 GBd Fibre Channel operation

- Supports 1.25 GBd Gigabit Ethernet (GE) operation

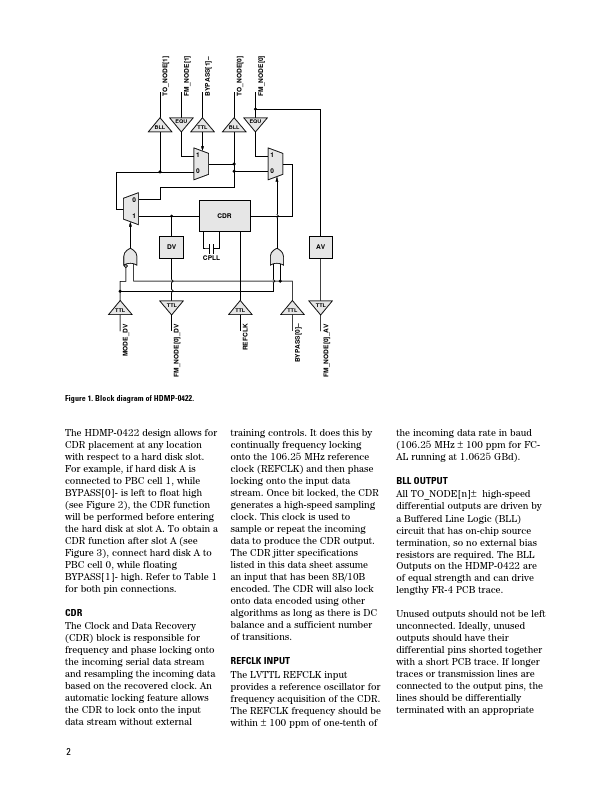

- Single PBC/CDR in one package

- CDR location determined by choice of cable input/output

- Amplitude valid and data valid detection (Fibre channel rate only) on FM_NODE[0] input

- Equalizers on all inputs

- High-speed LVPECL I/O

- Buffered Line Logic (BLL) outputs (no external bias resistors required)

- 0.46 W typical power at VCC = 3.3 V

- 24 Pin, low-cost SSOP package Applications

- RAID, JBOD, BTS cabinets

- One 2:1 muxes

- One...