HD74LVC373A

HD74LVC373A is Octal D-type Transparent manufactured by Hitachi Semiconductor.

Octal D-type Transparent Latches with 3-state Outputs

ADE-205-112B(Z) 3rd Edition December 1996 Description

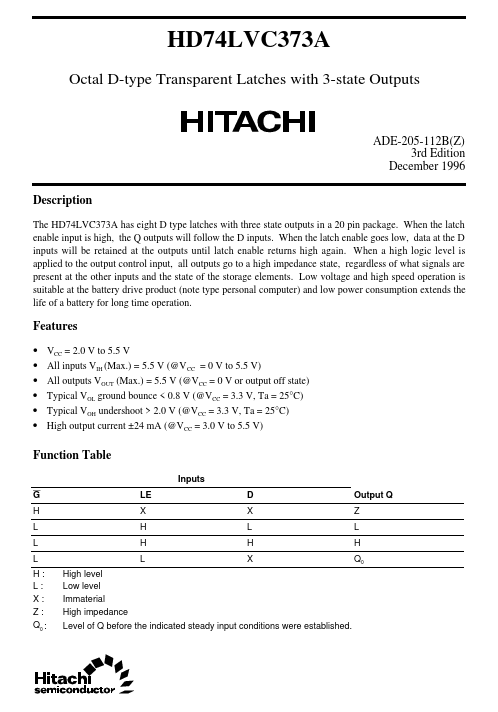

The HD74LVC373A has eight D type latches with three state outputs in a 20 pin package. When the latch enable input is high, the Q outputs will follow the D inputs. When the latch enable goes low, data at the D inputs will be retained at the outputs until latch enable returns high again. When a high logic level is applied to the output control input, all outputs go to a high impedance state, regardless of what signals are present at the other inputs and the state of the storage elements. Low voltage and high speed operation is suitable at the battery drive product (note...