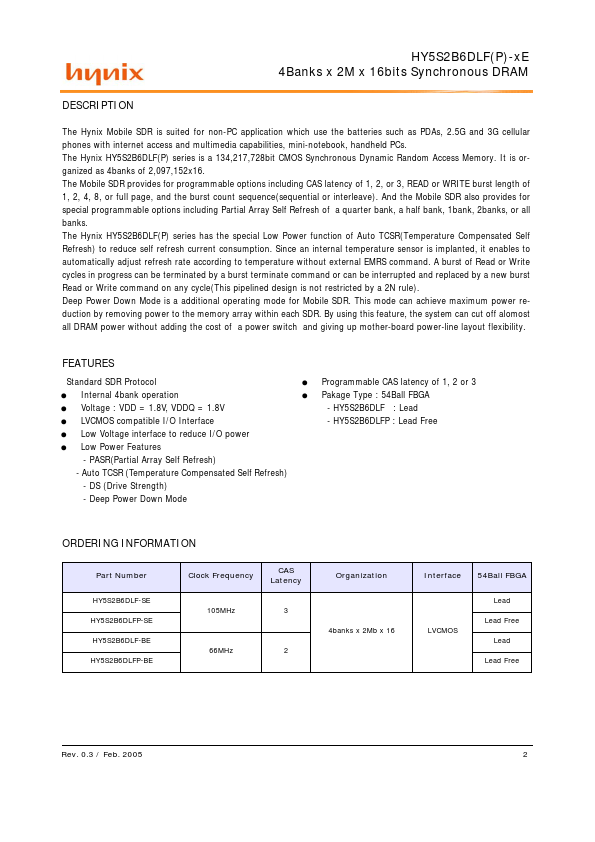

HY5S2B6DLF-BE Description

and is subject to change without notice. Hynix Semiconductor does not assume any responsibility for use of circuits described. No patent licenses are implied.

HY5S2B6DLF-BE Key Features

- Voltage : VDD = 1.8V, VDDQ = 1.8V

- LVCMOS patible I/O Interface

- Low Voltage interface to reduce I/O power

- Low Power Features

- PASR(Partial Array Self Refresh)

- Auto TCSR (Temperature pensated Self Refresh)

- DS (Drive Strength)

- Deep Power Down Mode

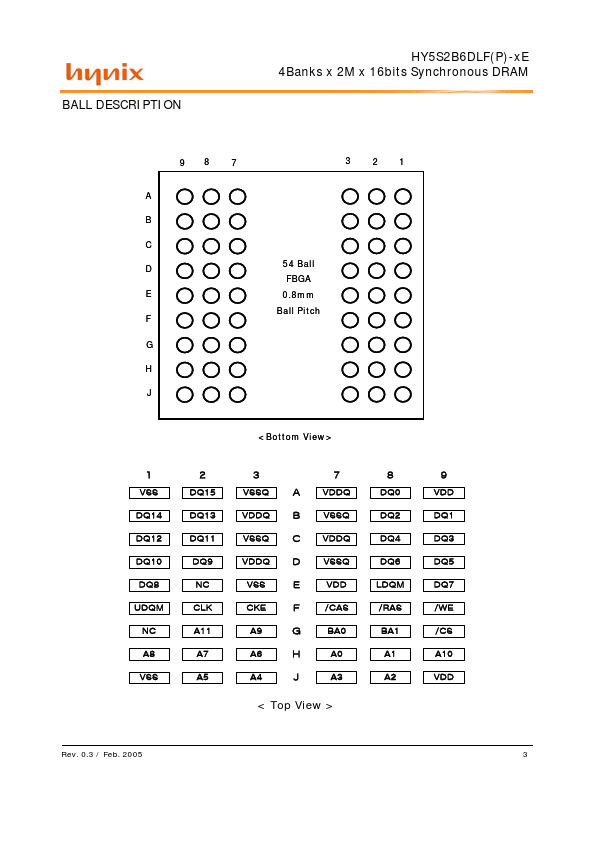

- Programmable CAS latency of 1, 2 or 3 Pakage Type : 54Ball FBGA

- HY5S2B6DLF : Lead