| Part | 9DBL0455 |

|---|---|

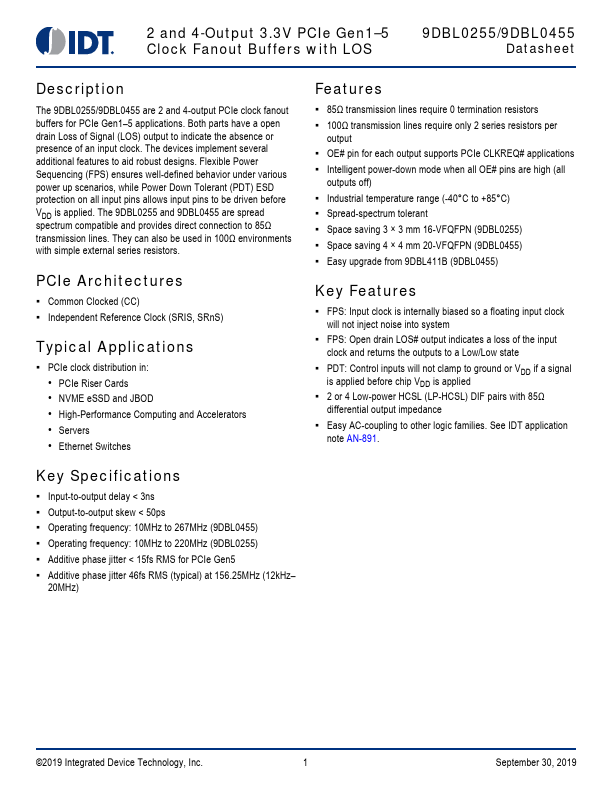

| Description | PCIe Gen1-5 Clock Fanout Buffers |

| Manufacturer | IDT |

| Size | 304.09 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| 9DBL0455 | Renesas | 2 and 4-Output 3.3V PCIe Gen1-5 Clock Fanout Buffers |

| 9DBL0452 | Renesas | 3.3V PCIe Zero Delay Buffer |

| 9DBL0452 | Renesas | Zero-Delay/Fanout Buffer |

| 9DBL0452C | Renesas | 2 to 8-Output 3.3V PCIe Zero-Delay/Fanout Buffers |