ICS889872

ICS889872 is DIFFERENTIAL-TO-LVDS BUFFER/DIVIDER W/INTERNAL TERMINATION manufactured by IDT.

..

PRELIMINARY

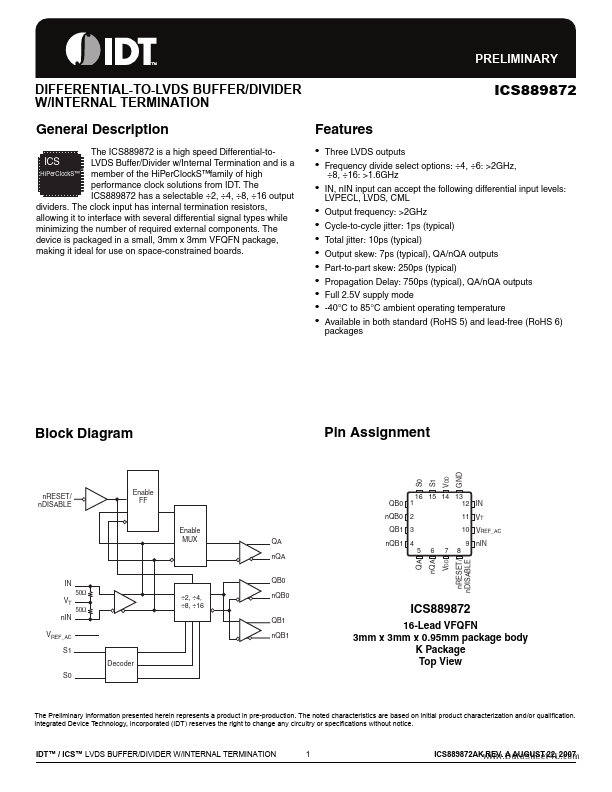

DIFFERENTIAL-TO-LVDS BUFFER/DIVIDER W/INTERNAL TERMINATION

ICS889872 Features

- -

- -

- -

- -

- -

- -

Three LVDS outputs Frequency divide select options: ÷4, ÷6: >2GHz, ÷8, ÷16: >1.6GHz IN, nIN input can accept the following differential input levels: LVPECL, LVDS, CML Output frequency: >2GHz Cycle-to-cycle jitter: 1ps (typical) Total jitter: 10ps (typical) Output skew: 7ps (typical), QA/nQA outputs Part-to-part skew: 250ps (typical) Propagation Delay: 750ps (typical), QA/nQA outputs Full 2.5V supply mode -40°C to 85°C ambient operating temperature Available in both standard (RoHS 5) and lead-free (RoHS 6) packages

General Description

The ICS889872 is a...