IDT71V546S Description

128K x 36, 3.3V Synchronous IDT71V546S SRAM with ZBT™.

IDT71V546S Key Features

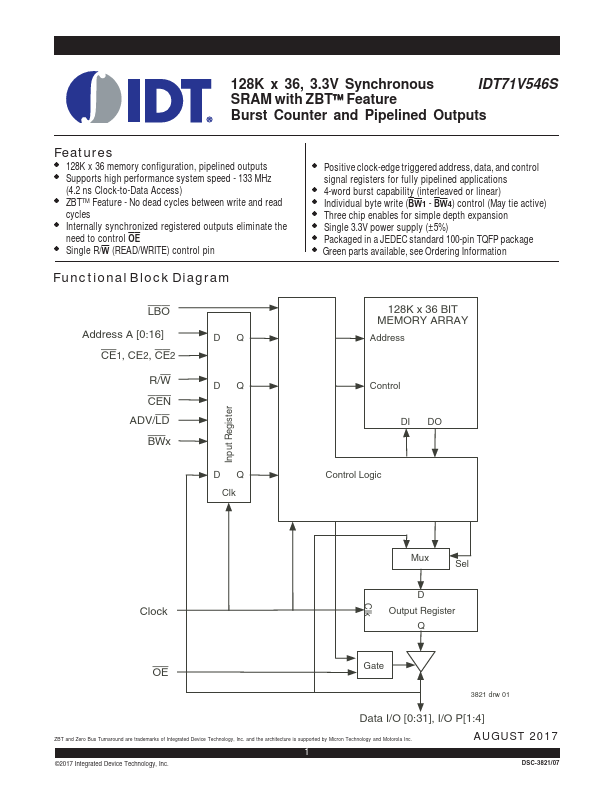

- 128K x 36 memory configuration, pipelined outputs

- Supports high performance system speed

- 133 MHz

- ZBTTM Feature

- No dead cycles between write and read

- Internally synchronized registered outputs eliminate the

- Single R/W (READ/WRITE) control pin

- Positive clock-edge triggered address, data, and control signal registers for fully pipelined