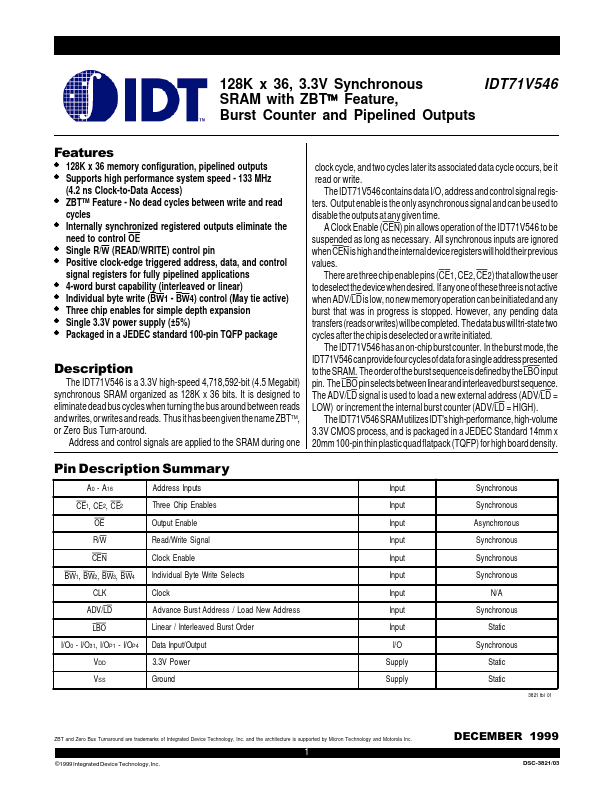

- Part: IDT71V546

- Description: 128K x 36/ 3.3V Synchronous SRAM with ZBT Feature/ Burst Counter and Pipelined Outputs

- Manufacturer: Integrated Device Technology

- Size: 178.20 KB

Datasheets by Manufacturer

- IDT71V546S — Renesas — Synchronous SRAM

- IDT71V547S — IDT — 3.3V Synchronous SRAM

- IDT71V547XS — IDT — 3.3V Synchronous SRAM