IS64WV25616LEBLL Overview

Description

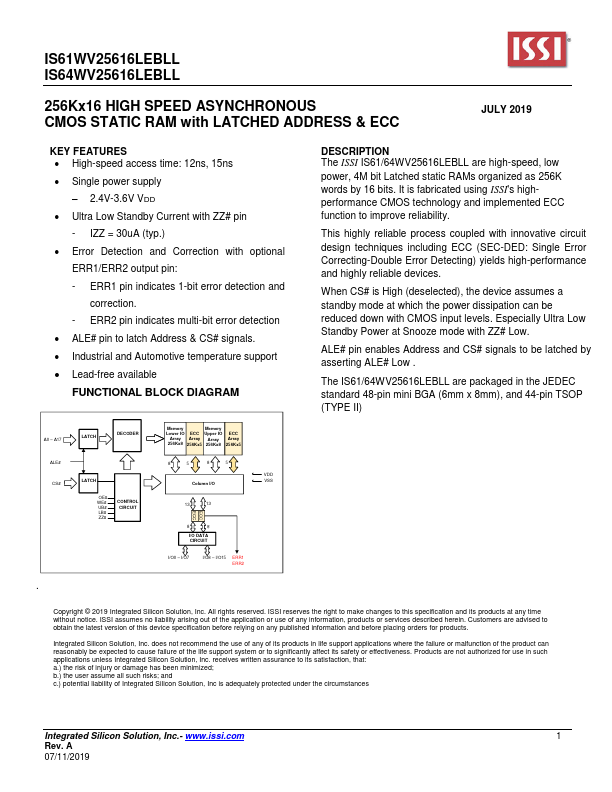

The ISSI IS61/64WV25616LEBLL are high-speed, low power, 4M bit Latched static RAMs organized as 256K words by 16 bits. It is fabricated using ISSI's highperformance CMOS technology and implemented ECC function to improve reliability.

Key Features

- High-speed access time: 12ns, 15ns

- Single power supply – 2.4V-3.6V VDD

- Ultra Low Standby Current with ZZ# pin

- IZZ = 30uA (typ.)

- Error Detection and Correction with optional ERR1/ERR2 output pin

- ERR1 pin indicates 1-bit error detection and correction

- ERR2 pin indicates multi-bit error detection

- ALE# pin to latch Address & CS# signals

- Industrial and Automotive temperature support