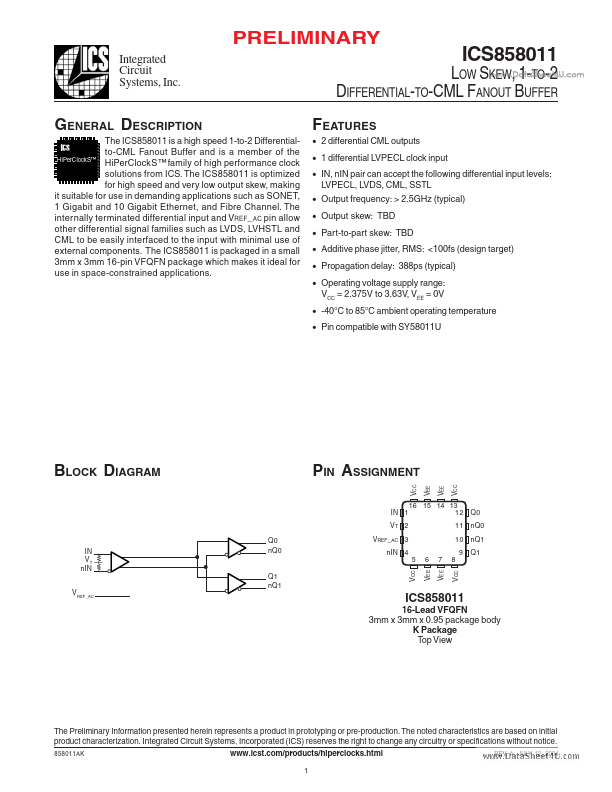

ICS858011 Key Features

- 2 differential CML outputs

- 1 differential LVPECL clock input

- IN, nIN pair can accept the following differential input levels: LVPECL, LVDS, CML, SSTL

- Output frequency: > 2.5GHz (typical)

- Output skew: TBD

- Part-to-part skew: TBD

- Additive phase jitter, RMS: <100fs (design target)

- Propagation delay: 388ps (typical)

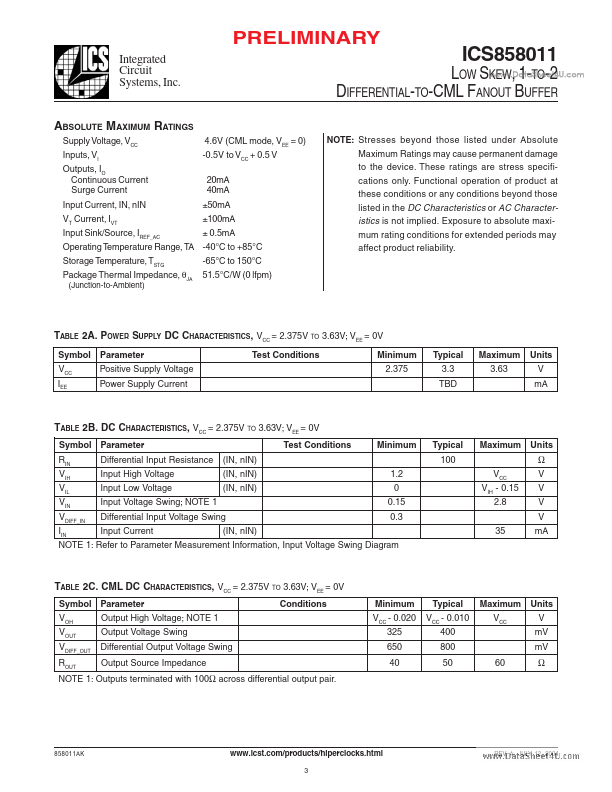

- Operating voltage supply range: VCC = 2.375V to 3.63V, VEE = 0V

- 40°C to 85°C ambient operating temperature