ICS93701 Datasheet Text

.DataSheet.co.kr

Integrated Circuit Systems, Inc.

ICS93701

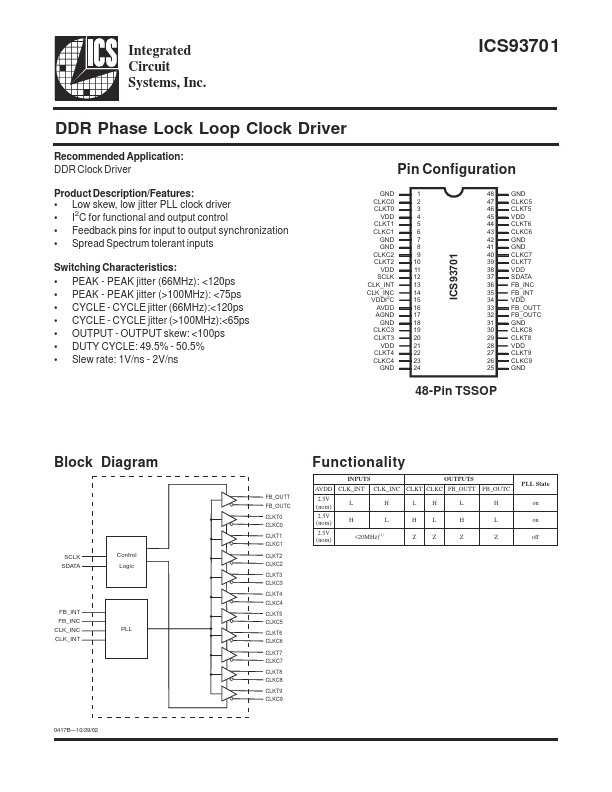

DDR Phase Lock Loop Clock Driver

Remended Application: DDR Clock Driver Product Description/Features

:

- Low skew, low jitter PLL clock driver

- I2C for functional and output control

- Feedback pins for input to output synchronization

- Spread Spectrum tolerant inputs Switching Characteristics:

- PEAK

- PEAK jitter (66MHz): <120ps

- PEAK

- PEAK jitter (>100MHz): <75ps

- CYCLE

- CYCLE jitter (66MHz):<120ps

- CYCLE

- CYCLE jitter (>100MHz):<65ps

- OUTPUT

- OUTPUT skew: <100ps

- DUTY CYCLE: 49.5%

- 50.5%

- Slew rate: 1V/ns

- 2V/ns

GND CLKC0 CLKT0 VDD CLKT1 CLKC1 GND GND CLKC2 CLKT2 VDD SCLK CLK_INT CLK_INC 2 VDDI C AVDD AGND GND CLKC3 CLKT3 VDD CLKT4 CLKC4 GND

Pin Configuration

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 GND CLKC5 CLKT5 VDD CLKT6 CLKC6 GND GND CLKC7 CLKT7 VDD SDATA FB_INC FB_INT VDD FB_OUTT FB_OUTC GND CLKC8 CLKT8 VDD CLKT9 CLKC9 GND

48-Pin TSSOP

Block Diagram

FB_OUTT FB_OUTC CLKT0 CLKC0 CLKT1 CLKC1...