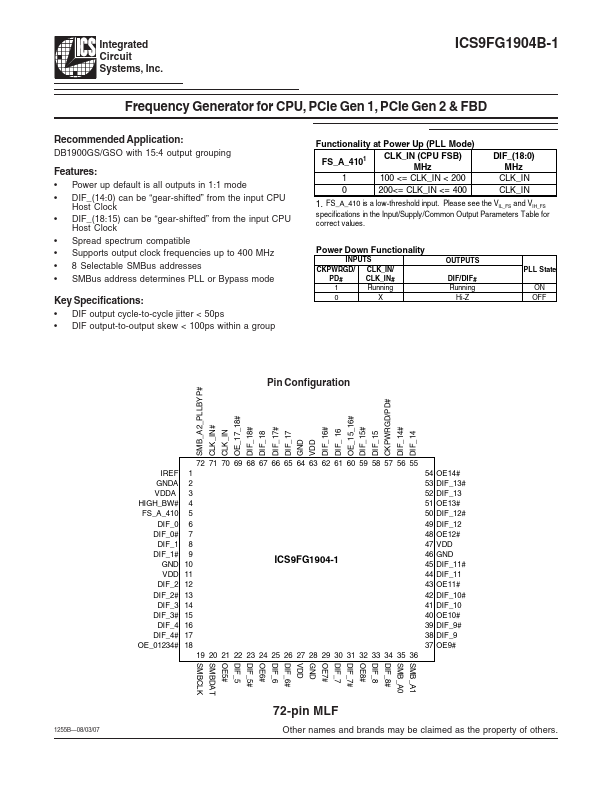

ICS9FG1904B-1 Overview

Key Features

- Power up default is all outputs in 1:1 mode

- DIF_(14:0) can be “gear-shifted” from the input CPU Host Clock

- DIF_(18:15) can be “gear-shifted” from the input CPU Host Clock

- Spread spectrum compatible

- Supports output clock frequencies up to 400 MHz

- 8 Selectable SMBus addresses

- SMBus address determines PLL or Bypass mode Key Specifications

- DIF output cycle-to-cycle jitter < 50ps