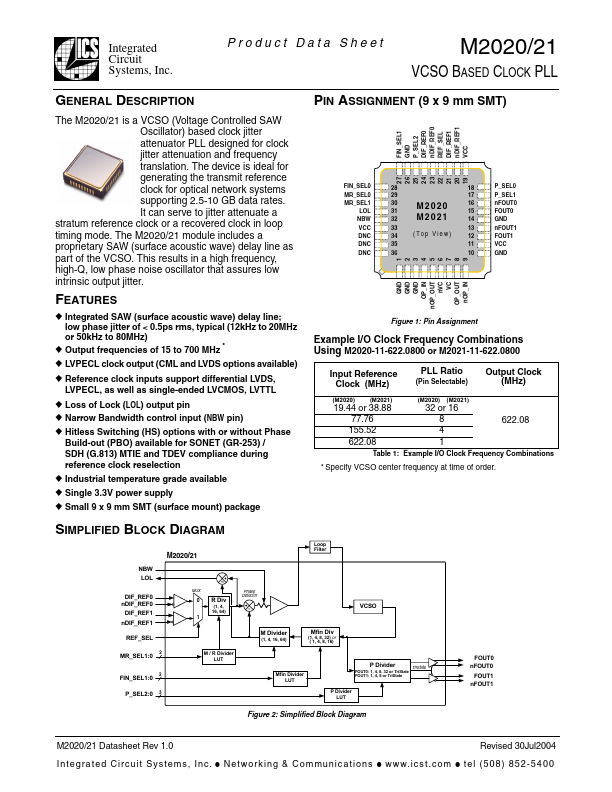

M2020-2021 Description

The M2020/21 is a VCSO (Voltage Controlled SAW Oscillator) based clock jitter attenuator PLL designed for clock jitter attenuation and frequency translation. The device is ideal for generating the transmit reference clock for optical network systems supporting 2.5-10 GB data rates. It can serve to jitter attenuate a stratum reference clock or a recovered clock in loop timing mode.

M2020-2021 Key Features

- Integrated SAW (surface acoustic wave) delay line; low phase jitter of < 0.5ps rms, typical (12kHz to 20MHz or 50kHz to

- Output frequencies of 15 to 700 MHz

- LVPECL clock output (CML and LVDS options available)

- Reference clock inputs support differential LVDS, LVPECL, as well as single-ended LVCMOS, LVTTL

- Loss of Lock (LOL) output pin

- Narrow Bandwidth control input (NBW pin)

- Hitless Switching (HS) options with or without Phase Build-out (PBO) available for SONET (GR-253) / SDH (G.813) MTIE and

- Industrial temperature grade available

- Single 3.3V power supply

- Small 9 x 9 mm SMT (surface mount) package