IDT23S05E

Description

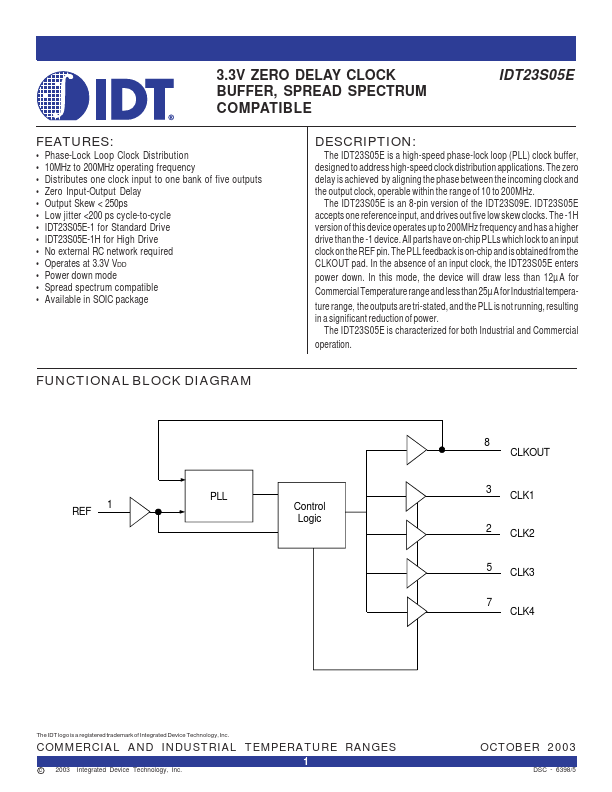

FUNCTIONAL 8 CLKOUT REF 1 PLL Control Logic 3 CLK1 2 CLK2 5 7 CLK3 CLK4 The IDT logo is a registered trademark of Integrated Device Technology, Inc.

Key Features

- The zero delay is achieved by aligning the phase between the ining clock and the output clock, operable within the range of 10 to 200MHz

- IDT23S05E accepts one reference input, and drives out five low skew clocks

- The -1H version of this device operates up to 200MHz frequency and has a higher drive than the -1 device

- All parts have on-chip PLLs which lock to an input clock on the REF pin

- The PLL feedback is on-chip and is obtained from the CLKOUT pad

- In the absence of an input clock, the IDT23S05E enters power down

- The IDT23S05E is characterized for both Industrial and mercial operation

Applications

- SDRAM Tele Data PC Motherboards/Workstations Critical Path Delay Designs