ICS854S013

ICS854S013 is 1-TO-3 DIFFERENTIAL-TO-LVDS FANOUT BUFFER manufactured by Integrated Device Technology.

PRELIMINARY

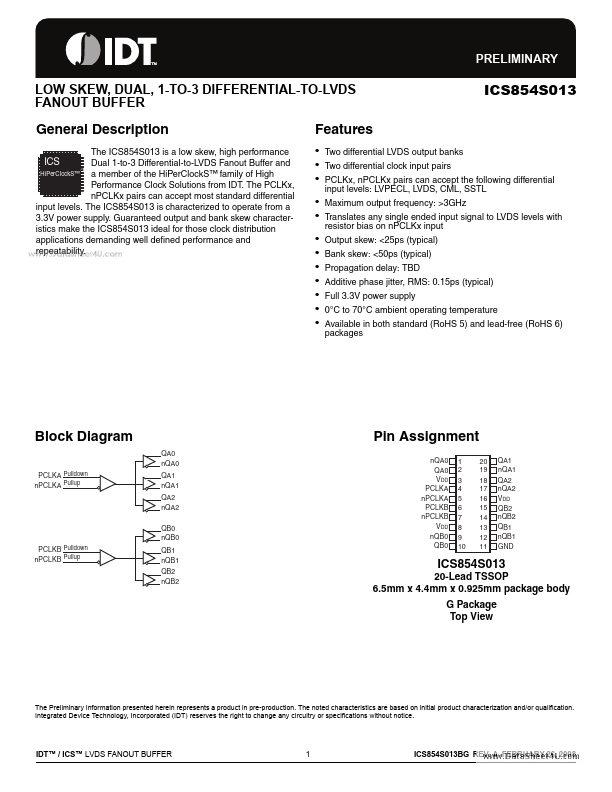

LOW SKEW, DUAL, 1-TO-3 DIFFERENTIAL-TO-LVDS FANOUT BUFFER

General Description

The ICS854S013 is a low skew, high performance Dual 1-to-3 Differential-to-LVDS Fanout Buffer and HiPerClockS™ a member of the HiPerClockS™ family of High Performance Clock Solutions from IDT. The PCLKx, nPCLKx pairs can accept most standard differential input levels. The ICS854S013 is characterized to operate from a 3.3V power supply. Guaranteed output and bank skew characteristics make the ICS854S013 ideal for those clock distribution applications demanding well defined performance and repeatability. ..

Features

- -

- -

- -

- -

- -

- -

Two differential LVDS output...