IDT70V37L Description

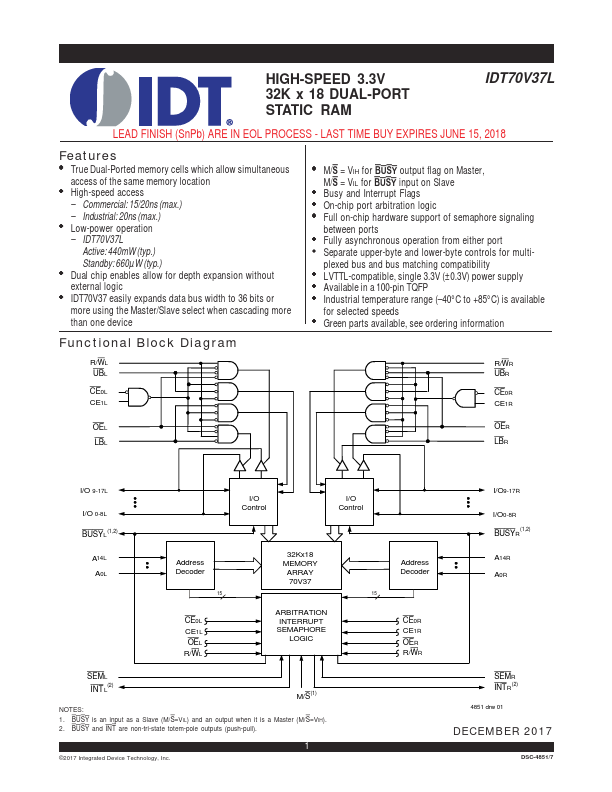

The IDT70V37 is a high-speed 32K x 18 Dual-Port Static RAM. The IDT70V37 is designed to be used as a stand-alone 576K-bit Dual-Port RAM or as a bination MASTER/SLAVE Dual-Port RAM for 36-bit-or-more word system. Using the IDT MASTER/SLAVE Dual-Port RAM approach in 36-bit or wider memory system applications results in full-speed, error-free operation without the need for additional discrete logic.