IDT74FCT388915T100

IDT74FCT388915T100 is 3.3V LOW SKEW PLL-BASED CMOS CLOCK DRIVER WITH manufactured by Integrated Device Technology.

- Part of the IDT-74FCT comparator family.

- Part of the IDT-74FCT comparator family.

IDT54/74FCT388915T 70/100/133/150 3.3V LOW SKEW PLL-BASED CLOCK DRIVER

MILITARY AND MERCIAL TEMPERATURE RANGES

Integrated Device Technology, Inc.

3.3V LOW SKEW PLL-BASED CMOS CLOCK DRIVER (WITH 3-STATE)

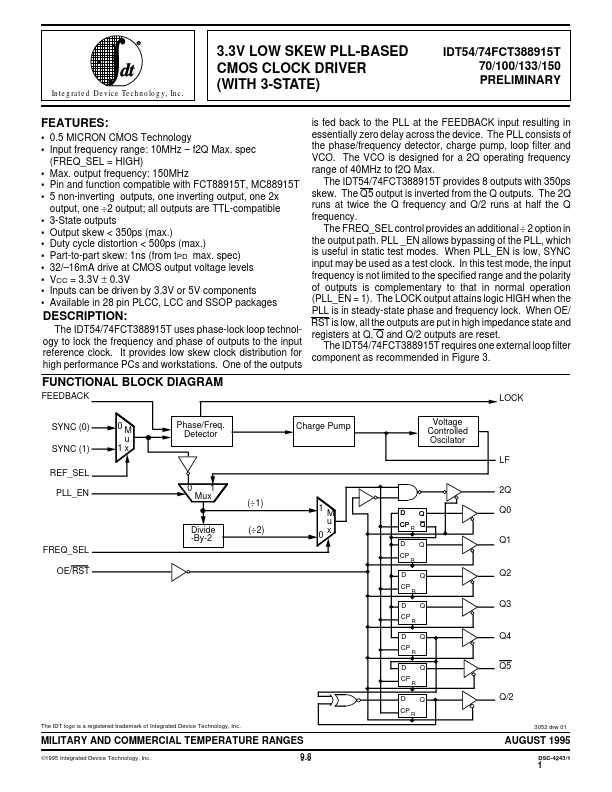

IDT54/74FCT388915T 70/100/133/150 PRELIMINARY is fed back to the PLL at the FEEDBACK input resulting in essentially zero delay across the device. The PLL consists of

- 0.5 MICRON CMOS Technology the phase/frequency detector, charge pump, loop filter and

- Input frequency range: 10MHz

- f2Q Max. spec VCO. The VCO is designed for a 2Q operating frequency (FREQ_SEL = HIGH) range of 40MHz to f2Q Max.

- Max. output frequency: 150MHz The IDT54/74FCT388915T provides 8 outputs with 350ps

- Pin and function patible with FCT88915T, MC88915T skew. The Q5 output is inverted from the Q outputs. The 2Q

- 5 non-inverting outputs, one inverting output, one 2x runs at twice the Q frequency and Q/2 runs at half the Q output, one ÷ 2 output; all outputs are TTL-patible frequency.

- 3-State outputs The FREQ_SEL control provides an additional ÷ 2 option in

- Output skew < 350ps (max.) the output path. PLL _EN allows bypassing of the PLL, which

- Duty cycle distortion < 500ps (max.) is useful in static test modes. When PLL_EN is low, SYNC

- Part-to-part skew: 1ns (from t PD max. spec) input may be used as a test clock. In this test mode, the input

- 32/- 16m A drive at CMOS output voltage levels frequency is not limited to the specified range and the polarity

- VCC = 3.3V ± 0.3V of outputs is plementary to that in normal operation

- Inputs can be driven by 3.3V or 5V ponents (PLL_EN = 1). The LOCK output attains logic HIGH when the

- Available in 28 pin PLCC, LCC and SSOP packages PLL is in steady-state phase and frequency lock. When OE/ DESCRIPTION: RST is low, all the outputs are put in high impedance state and The IDT54/74FCT388915T uses phase-lock loop technol- registers at Q, Q and Q/2 outputs are reset. ogy to lock the frequency and phase of outputs to the input...